DFT Tools

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Conclusion and Summary

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In summary, we’ve discussed several DFT tools like the Synopsys DFT Compiler, Cadence Modus, and Mentor Graphics Tessent. Each plays a unique role in enhancing testability. Let’s recap: why are these tools essential?

They make testing easier and more efficient while helping to find defects early!

Correct! Remember, DFT tools allow us to automate processes and improve fault coverage, which ultimately lowers manufacturing costs. Great discussion today, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The DFT tools discussed in this section play a critical role in facilitating various DFT techniques, such as scan chain insertion, built-in self-test (BIST), and boundary scan. These tools enhance the testability of designs, contributing to improved chip performance and reduced manufacturing costs.

Detailed

DFT Tools

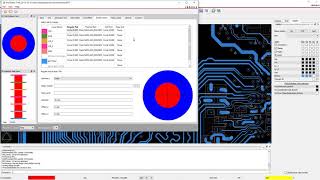

Design for Testability (DFT) tools are crucial in enabling the efficient implementation of DFT techniques during the VLSI design process. These electronic design automation (EDA) tools assist designers in incorporating features that facilitate easier testing, ensuring that chips can be thoroughly verified for functionality after fabrication. Key tools mentioned in this section include:

- Synopsys DFT Compiler: This tool is instrumental in inserting scan chains, applying test patterns, and preparing designs for testing, streamlining the process of enhancing chip testability.

- Cadence Modus: Modus offers comprehensive DFT solutions, including automatic test pattern generation (ATPG) and support for BIST, helping to optimize the testing process efficiently.

- Mentor Graphics Tessent: Widely utilized for scan insertion and test generation, Tessent also conducts fault coverage analysis to ensure that design tests are effective.

These tools not only improve testing efficiency but also help in identifying defects early in the design cycle, eventually leading to better overall chip quality and lower production costs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to DFT Tools

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Several EDA tools assist with DFT implementation:

Detailed Explanation

In this section, we start by introducing Electronic Design Automation (EDA) tools. These tools are essential in helping engineers implement DFT techniques effectively. They automate various tasks, making the design process more efficient.

Examples & Analogies

Think of EDA tools like the various appliances in a kitchen. Just as a blender, oven, and microwave help a chef prepare a meal quickly and efficiently, EDA tools help engineers streamline the design and testing of chips.

Synopsys DFT Compiler

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Synopsys DFT Compiler: This tool is used for inserting scan chains, applying test patterns, and preparing designs for test.

Detailed Explanation

The Synopsys DFT Compiler is a pivotal tool in the DFT process. It enables engineers to insert scan chains into the chip design. Scan chains are critical for testing because they allow internal signals to be accessed and tested systematically. The tool also helps apply test patterns that the chip must pass to verify its functionality.

Examples & Analogies

Imagine the DFT Compiler as a tool in a factory assembly line that checks every piece before it moves on to the next stage. It ensures the parts fit correctly and function as intended, just like the DFT Compiler ensures that the design can be adequately tested.

Cadence Modus

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Cadence Modus: Modus provides comprehensive DFT solutions, including scan insertion, automatic test pattern generation (ATPG), and BIST support.

Detailed Explanation

Cadence Modus is another powerful EDA tool that supports various DFT processes. It not only helps with inserting scan chains but also automates the generation of test patterns through a method called Automatic Test Pattern Generation (ATPG). This tool is particularly beneficial as it reduces manual efforts and increases the reliability of testing. Additionally, it supports Built-In Self-Test (BIST), which allows chips to test themselves, enhancing the overall efficiency of the testing process.

Examples & Analogies

Think of Cadence Modus like a smart oven that not only cooks your food but also automatically adjusts the temperature and time for different recipes. It simplifies the cooking process much like how the tool simplifies and automates DFT tasks.

Mentor Graphics Tessent

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Mentor Graphics Tessent: Tessent is widely used for scan insertion, test generation, and fault coverage analysis, ensuring that designs can be efficiently tested.

Detailed Explanation

Mentor Graphics Tessent is a comprehensive DFT tool that specializes in scan insertion and test generation. One of its significant features is fault coverage analysis, which evaluates how well the testing strategies can detect potential faults in the chip design. This analysis is crucial because it helps ensure that most, if not all, defects can be caught before the chip is released into production.

Examples & Analogies

Imagine Tessent as a quality inspector who thoroughly checks every toy on a production line to ensure it meets safety standards before being sold. This ensures that defective toys don’t reach customers, just like how Tessent ensures that defective chips are identified before they hit the market.

Key Concepts

-

Design for Testability Tools: Tools used to implement various techniques that improve testability.

-

Synopsys DFT Compiler: A tool that inserts scan chains and prepares designs for testing.

-

Cadence Modus: Offers comprehensive DFT solutions including ATPG.

-

Mentor Graphics Tessent: Tool for scan insertion and fault coverage.

Examples & Applications

Using Synopsys DFT Compiler, designers can automate the insertion of scan chains, which simplifies the testing of complex VLSI designs.

Cadence Modus helps in generating specific test patterns based on design requirements, improving the efficiency of the testing phase.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

For every test and every play, the tools help us find faults that stray.

Stories

Imagine a chip going to a test party; it wears its flashy scan chains to reveal secrets inside, ensuring it shines and earns praise from all the designers.

Memory Tools

Remember the mnemonic 'S-D-C' for Synopsys, DFT Compiler.

Acronyms

DFT - Designs For Testing

Flash Cards

Reference links

Supplementary resources to enhance your learning experience.