Design for Manufacturability (DFM)

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of DFM

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're discussing the importance of Design for Manufacturability, or DFM. Can anyone tell me why optimizing a design for manufacturing might benefit a company?

It seems like it would help reduce costs.

Exactly! Cost reduction is a significant benefit of DFM. By minimizing defects and rework, companies can save money. Can anyone think of another advantage?

Improving yield is probably another reason.

Absolutely! Improving yield means more successful chips are fabricated from each wafer, which is critical for profitability. Great work, everyone!

Key DFM Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's discuss some key DFM techniques. Can anyone tell me what Design Rule Checking, or DRC, involves?

Isn't it about checking if the design follows the specific rules for feature sizes?

Correct! DRC ensures compliance with manufacturing standards to prevent defects. Now, why might minimizing process variation be critical?

It helps the circuit function reliably despite the inevitable variations in manufacturing?

Exactly! Minimizing sensitivity to process variations is key to robust designs. Well done!

DFM Tools

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

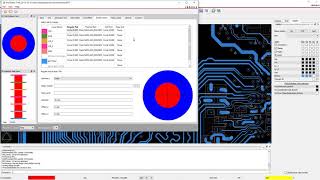

Now let's examine some EDA tools that facilitate DFM. Can anyone name a tool and explain what it does?

Cadence Allegro helps optimize designs to minimize errors.

Great answer! What about Mentor Graphics Calibre?

It focuses on layout optimization and manufacturability, right?

Exactly! These tools are essential for developers to ensure their designs are ready for efficient manufacturing. Keep up the good effort!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The DFM principles aim to reduce manufacturing costs, improve chip yield, and ensure products meet performance and quality standards. By implementing techniques such as Design Rule Checking and minimizing process variations, designers can enhance manufacturability throughout the design process.

Detailed

Design for Manufacturability (DFM)

Design for Manufacturability (DFM) is a critical aspect of the chip design process that emphasizes creating designs which are optimized for the manufacturing environment. The overarching goal of DFM is to facilitate an efficient, cost-effective, and high-quality production of semiconductor products.

Importance of DFM

- Cost Reduction: DFM helps in minimizing the manufacturing costs by ensuring that designs are conducive to the production process, thus reducing defects and the necessity for expensive rework.

- Yield Improvement: By designing robust systems that can withstand manufacturing process variations better, DFM contributes to a higher proportion of functional chips being produced from each wafer.

- Faster Time-to-Market: Efficient DFM practices shorten the duration of the manufacturing process, enabling quicker fabrication and delivery to the market.

Key DFM Techniques

- Design Rule Checking (DRC): Ensures the design complies with minimum feature sizes and spacing required by manufacturing processes to avoid defects.

- Minimizing Process Variations: Focuses on creating circuits that are less sensitive to fabrication variability by optimizing design margins.

- Minimizing Interconnect Length: The design is optimized to reduce interconnects, which helps mitigate delays and signal degradation.

- Via Optimization: Minimizes excessive via usage to reduce resistance and capacitance affecting performance.

- Cell and Layout Optimization: Utilizes standard cells to simplify manufacturing and increase yield.

- Hotspot Analysis: Identifies and optimizes areas in the design that could lead to overheating or reliability issues.

DFM Tools

EDA tools such as Cadence Allegro, Mentor Graphics Calibre, and Synopsys IC Validator assist in DFM by addressing layout and interconnect issues which can compromise manufacturability.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of DFM

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Design for Manufacturability (DFM) focuses on ensuring that the design is optimized for the manufacturing process. The goal is to make the design easy and cost-effective to manufacture, while ensuring that the final product meets all performance, quality, and reliability standards. DFM principles are applied throughout the design process to minimize defects, reduce variation, and improve yield.

Detailed Explanation

DFM is a methodology used in the design of products, particularly in electronics manufacturing, which aims to streamline and simplify the manufacturing process. The primary intent is to create designs that are not just functional but also inherently suitable for mass production. This involves considering various factors such as material usage, design complexity, and manufacturability throughout the design phase, thereby reducing the possibility of defects and enhancing yield rates. Defects refer to flaws or errors in the manufacturing process, while yield refers to the ratio of functional products compared to total produced. Doing so leads to a smoother transition from the design phase to the fabrication of the product.

Examples & Analogies

Think of DFM like baking cookies. If you have a clear, straightforward recipe that requires common ingredients, it's likely that you'll succeed in making delicious cookies. However, if your recipe calls for complex techniques and hard-to-find ingredients, the chances of making a successful batch decrease. Similarly, in manufacturing, a simpler design (like a cookie recipe) leads to fewer errors in production, resulting in a higher 'yield' or number of good cookies.

Importance of DFM

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Cost Reduction: DFM techniques help reduce manufacturing costs by optimizing the design for the process, reducing the likelihood of defects and the need for expensive rework.

● Yield Improvement: By ensuring the design is robust to process variations, DFM improves the yield, ensuring a higher percentage of functional chips from a wafer.

● Faster Time-to-Market: DFM reduces the time spent in the manufacturing process by ensuring that designs are ready for fabrication with minimal issues.

Detailed Explanation

DFM is crucial for several reasons. First, it helps in 'Cost Reduction' by making designs simpler and easier to manufacture. This, in turn, minimizes mistakes that could lead to costly rework or scrapping of defective products. Next, through 'Yield Improvement', the designs are configured to be less sensitive to manufacturing variations, meaning that more good, usable chips will come from each production batch. Lastly, 'Faster Time-to-Market' is achieved asoptimized designs can be produced quicker, ensuring that products reach consumers sooner, giving companies a competitive edge.

Examples & Analogies

Consider a car manufacturing assembly line. If the design of the car is complicated, workers may take longer to assemble it, leading to delays (longer time-to-market) and potential mistakes (higher costs and lower yield). However, if the car is designed with assembly in mind, using compatible parts that fit together easily, the line runs smoothly, producing cars efficiently and profitably.

Key DFM Techniques

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Design Rule Checking (DRC): DRC ensures that the design meets the minimum feature sizes and spacing requirements for the manufacturing process. DRC violations can lead to defects during fabrication, and DFM aims to reduce or eliminate such violations.

● Minimizing Process Variations: DFM involves designing circuits that are less sensitive to variations in the manufacturing process, such as variations in transistor sizes, line widths, and doping levels. This can involve adjusting design margins and optimizing layout geometry to account for these variations.

● Minimizing Interconnect Length: DFM seeks to reduce the length of interconnects, as longer interconnects are more prone to delays, signal degradation, and power consumption. By optimizing the routing of interconnects, the design is made more manufacturable and reliable.

● Via Optimization: In VLSI designs, vias are used to connect different metal layers. Excessive via usage can increase the resistance and capacitance of interconnects, leading to power loss and performance degradation. DFM aims to minimize via usage by optimizing the layout.

● Cell and Layout Optimization: Using compact, standardized cells in the design and optimizing their placement can reduce the number of defects and ensure that the chip is easier to manufacture. Standardized cells also help in making sure that they fit within the manufacturing process constraints.

● Hotspot Analysis: DFM tools analyze potential "hotspots" in the layout—areas where high current, heat, or power may cause reliability issues. By optimizing these regions, designers can prevent reliability issues in the final product.

Detailed Explanation

Key DFM techniques provide specific actions and tools for achieving manufacturability:

- Design Rule Checking (DRC) prevents design errors before fabrication.

- Minimizing Process Variations addresses inconsistencies in manufacturing by designing circuits that can tolerate some variability.

- Minimizing Interconnect Length reduces distance signals have to travel, improving performance.

- Via Optimization streamlines connections between layers to enhance speed and reduce errors.

- Cell and Layout Optimization ensures that designs are compact and standardized, making them easier to produce.

- Hotspot Analysis identifies areas prone to overheating or stress, allowing for early mitigation of potential failures. Together, these techniques create a comprehensive strategy for robust chip manufacturing.

Examples & Analogies

Imagine a city planning a highway system. Engineers would want to check boundaries (similar to DRC) to avoid building highways too close to residential areas, which could cause noise and pollution. They'll design to minimize bottlenecks (like minimizing interconnect lengths) and ensure that where highways intersect, the flow remains smooth to avoid traffic jams (like optimizing vias). All these considerations ensure efficient transportation, just as DFM strategies ensure efficient chip production.

DFM Tools

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

EDA tools assist with DFM to ensure that the design is optimized for manufacturing:

● Cadence Allegro: Allegro provides tools for DFM analysis and optimization, helping to minimize design errors and improve manufacturability.

● Mentor Graphics Calibre: Calibre offers DFM tools that focus on checking and optimizing the layout for manufacturability and yield enhancement.

● Synopsys IC Validator: This tool helps detect and fix DFM issues related to layout, interconnects, and process variations.

Detailed Explanation

Automatic design tools are crucial in implementing DFM principles efficiently. For instance, Cadence Allegro analyzes designs to identify potential manufacturing problems, optimizing layouts for easier production. Mentor Graphics Calibre focuses specifically on detecting layout errors based on DFM criteria to enhance overall yield. Similarly, Synopsys IC Validator helps in rectifying any issues that might arise from the design layout or interconnects, ensuring that the chip will be manufacturable without defects. These tools streamline the design process, making it easier for engineers to incorporate DFM principles.

Examples & Analogies

Consider these tools as smart assistants for an architect designing a building. Just as architects may use software that catches code violations or suggests better layouts, DFM software helps electronic designers avoid common manufacturing pitfalls, ensuring that the final product is not just innovative but also practical to mass-produce.

Key Concepts

-

Cost Reduction: DFM techniques lead to lower manufacturing costs by minimizing defects.

-

Yield Improvement: Optimizing the design leads to a higher yield rate of functional chips.

-

Design Rule Checking (DRC): Ensuring compliance with manufacturing standards to avoid defects.

-

Via Optimization: Reducing excessive via usage to enhance performance.

-

Hotspot Analysis: Identifying critical areas in a layout that may lead to reliability issues.

Examples & Applications

DRC can prevent defects by ensuring that the design does not violate minimum feature size requirements.

A robust design that minimizes process variation may maintain functionality despite fluctuations in manufacturing parameters.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

With DFM in mind, make it easy to find, designs that don't break, will surely awake!

Stories

Imagine a factory with a team of designers working hard. They implement DFM principles, and soon their products roll out smoothly, with high functionality and low defects, pleasing their customers!

Memory Tools

Remember the acronym 'CYP': Cost reduction, Yield improvement, and Product reliability.

Acronyms

Use 'DRY HOT' – Design Rule Checking, Reducing variation, Yield improvement, Hotspot Analysis, Optimizing vias, and Time to market.

Flash Cards

Glossary

- Design for Manufacturability (DFM)

A design approach that seeks to optimize the manufacturing process to ensure product quality, reduce costs, and improve yield.

- Design Rule Checking (DRC)

A process used to ensure that the design complies with specific manufacturing rules and standards.

- Yield

The proportion of functional products produced from manufacturing relative to the total number produced.

- Via Optimization

Techniques used to minimize the number of vias in a circuit to reduce performance issues.

- Hotspot Analysis

The identification and assessment of areas in a design that may lead to overheating or reliability problems.

Reference links

Supplementary resources to enhance your learning experience.