Design for Testability (DFT)

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of DFT

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will explore the importance of Design for Testability, or DFT. Can anyone share why minimizing test costs might be crucial in chip design?

It's important because lower testing costs can make the overall production cheaper.

Exactly, and it allows manufacturers to allocate resources more efficiently. DFT also ensures that chips function as expected. Why do you think that is important?

If we don't know if a chip works, it could lead to failures in end products.

Right! Ensuring functionality can prevent costly recalls and enhance customer satisfaction. DFT also improves yield by catching faults early. Can someone remind me what yield means in this context?

Yield refers to the percentage of chips that are functional after the manufacturing process.

Great job! The higher the yield, the better for profitability. Let's summarize: DFT minimizes costs, ensures functionality, and improves yield.

Key DFT Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we've discussed why DFT is essential, let's look at some key techniques. First up is scan chain insertion. Can anyone explain what this involves?

It's adding extra flip-flops that allow access to internal signals for testing purposes.

Exactly! This method makes it easier to load test vectors. What about Built-In Self-Test, or BIST? How does it benefit the testing process?

BIST lets the chip test itself, which can save time and resources during manufacturing.

Exactly, and this is especially useful in embedded systems. Does anyone know what boundary scan or JTAG stands for?

It stands for Joint Test Action Group, right?

Correct! It helps test interconnects, which is crucial. Lastly, can you tell me why at-speed testing is important?

Because it detects timing issues that might not show at slower speeds.

Exactly! That wraps up our key techniques. Remember, these methods enhance testability significantly.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

DFT involves implementing various strategies during the design process to improve the ease and cost of testing chips after fabrication. This section highlights its importance in minimizing test costs, ensuring functionality, and improving yield, along with various DFT techniques, tools, and methods.

Detailed

Design for Testability (DFT)

Design for Testability (DFT) encompasses strategies and techniques implemented during the chip design process, aimed at making the testing of chip functionality easier and more cost-effective. The primary goal of DFT is to catch defects early in production, thereby minimizing overall costs and ensuring high-quality outcomes.

Importance of DFT

DFT plays a crucial role in several aspects:

- Minimize Test Costs: By incorporating efficient methods for defect detection, DFT significantly reduces testing expenses.

- Ensure Functionality: DFT enables the incorporation of test structures that enhance observability and controllability of internal signals, allowing for thorough checks of the design’s functionality.

- Improved Yield: Early fault detection in manufacturing enhances the yield of functional chips, lowering the number of rejects and improving cost efficiency.

Key DFT Techniques

Highlighted techniques include:

- Scan Chain Insertion: Adding flip-flops to create a scan chain that simplifies signal access and logic testing.

- Built-In Self-Test (BIST): Embedding self-test capabilities within the chip for automated testing both during manufacturing and throughout the product life cycle.

- Boundary Scan (JTAG): A standard for testing interconnections between chips, identifying faults in connections and components.

- At-Speed Testing: Testing chips at operational clock speeds to identify timing-related faults.

- Fault Simulation: Simulating various faults to evaluate the effectiveness of testing strategies in fault detection.

DFT Tools

Various EDA tools support DFT implementation, including:

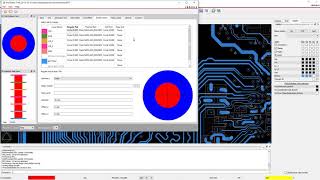

- Synopsys DFT Compiler for scan chains and test preparation.

- Cadence Modus for comprehensive DFT solutions.

- Mentor Graphics Tessent for scan insertion and test generation.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Definition of DFT

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Design for Testability (DFT) refers to the techniques and strategies implemented during the design process to make it easier and more cost-effective to test the functionality and performance of a chip during production. The goal of DFT is to ensure that the chip can be thoroughly tested after fabrication, catching defects early and minimizing production costs.

Detailed Explanation

Design for Testability (DFT) involves applying specific techniques while designing chips to facilitate easier testing. This means that during the design phase, engineers consider how the chip will be tested once it is built. The primary aim is to ensure that potential issues can be identified quickly and inexpensively once the chip is finished. By using DFT methods, manufacturers can identify defects that need fixing right away, which ultimately helps in keeping the costs of production lower because issues can be addressed before mass manufacturing.

Examples & Analogies

Imagine you are baking cookies. If you have a special tool that allows you to check if the dough is properly mixed or if the right amount of sugar is used while you’re making them, it saves you from baking a dozen cookies and discovering they taste bad afterward. Similarly, DFT acts as a 'testing tool' in chip design to ensure quality and functionality before it goes into full production.

Importance of DFT

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Importance of DFT

- Minimize Test Costs: DFT helps in reducing the cost of testing by providing efficient and automated methods for detecting manufacturing defects.

- Ensure Functionality: By incorporating test structures and ensuring observability and controllability of the internal signals, DFT helps verify that the design functions as expected.

- Improved Yield: DFT techniques help improve yield by detecting faulty chips early in the manufacturing process, reducing the number of defective units.

Detailed Explanation

The importance of DFT lies in its three main benefits: First, it significantly reduces testing costs by automating defect detection methods, making the process faster and less expensive. Second, it ensures that the chips function correctly by implementing mechanisms during the design phase that verify the internal signals are manageable and can be monitored. Lastly, DFT can lead to better overall yield during production by catching errors early. This means fewer units are scrapped, leading to more functional chips produced from each batch.

Examples & Analogies

Think about quality control in a factory that produces toys. If they check the toys at various stages of production rather than just at the end, they save money by preventing a large batch of defective toys from being sent out to stores. Similarly, DFT acts as quality assurance for chips, ensuring they pass various tests throughout their lifecycle, hence saving resources and improving overall output.

Key DFT Techniques

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Key DFT Techniques

Several DFT techniques are used to make chips more testable:

- Scan Chain Insertion: One of the most common DFT techniques, scan chains involve adding extra flip-flops to the design to enable access to internal signals. These flip-flops are connected in a series (scan chain) to allow for easier testing of the chip. The scan chains are used to load test vectors and capture output values, enabling testing of the design’s logic.

- Built-In Self-Test (BIST): BIST involves embedding test logic into the chip to enable it to test itself. BIST can perform automated testing during the manufacturing process or in-field testing during the product's life cycle. This technique is particularly useful in embedded systems and high-reliability applications.

- Boundary Scan (JTAG): Boundary scan, also known as JTAG (Joint Test Action Group), is a standard that allows for testing the interconnects between chips and components. It uses a shift register chain to scan the boundaries of each chip and helps detect issues like faulty connections or missing components.

- At-Speed Testing: At-speed testing involves testing the chip at the operational clock speed, which is essential for detecting timing-related faults that might not appear at slower speeds. It’s used to detect faults that occur due to timing violations or signal integrity issues.

- Fault Simulation: This technique simulates various faults in the design to assess how well the chip can be tested and to determine the effectiveness of the test strategies in detecting faults.

Detailed Explanation

DFT incorporates several critical techniques designed to facilitate effective testing:

1. Scan Chain Insertion allows internal chip signals to be monitored by interconnecting flip-flops in a sequence, facilitating easier testing.

2. Built-In Self-Test (BIST) lets the chip run its own tests, enabling it to identify issues autonomously, which is especially handy for high-importance applications.

3. Boundary Scan (JTAG) enables testing of connections between components, helping ensure there are no faults or weak links in how they interact.

4. At-Speed Testing tests the chip under actual operational speeds, uncovering timing issues before the chip is deployed.

5. Fault Simulation runs hypothetical faulty scenarios to understand potential weaknesses in the design and evaluate the effectiveness of the other DFT techniques used.

Examples & Analogies

Imagine a car manufacturer testing their vehicles before they hit the market. They simulate real-world driving conditions, check if all systems are operational, and ensure everything works as intended—including brakes, electronics, and safety features. Each technique in DFT acts like various testing methods for these cars, checking different functionalities to ensure a reliable and successful 'launch' of new chips.

DFT Tools

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

DFT Tools

Several EDA tools assist with DFT implementation:

- Synopsys DFT Compiler: This tool is used for inserting scan chains, applying test patterns, and preparing designs for test.

- Cadence Modus: Modus provides comprehensive DFT solutions, including scan insertion, automatic test pattern generation (ATPG), and BIST support.

- Mentor Graphics Tessent: Tessent is widely used for scan insertion, test generation, and fault coverage analysis, ensuring that designs can be efficiently tested.

Detailed Explanation

EDA (Electronic Design Automation) tools are essential for implementing DFT effectively. Examples include the Synopsys DFT Compiler, which helps integrate testing mechanisms into designs. Cadence Modus is another powerful tool, offering comprehensive features to enhance testability, like automatic test pattern generation. Lastly, Mentor Graphics Tessent is a strong tool for scan insertion and fault analysis, ensuring that designs can undergo thorough testing to verify their reliability.

Examples & Analogies

Consider a chef who uses specialized tools to chop, mix, and measure ingredients efficiently. Each tool simplifies a specific task in the cooking process, leading to a better overall dish. Similarly, DFT tools serve as specialized 'kitchen equipment' for engineers, simplifying the process of preparing chip designs for effective testing.

Key Concepts

-

Minimize Test Costs: DFT reduces costs associated with testing by implementing effective strategies.

-

Ensure Functionality: Ensuring that chips have the intended functionality through rigorous design and testing.

-

Improved Yield: DFT techniques improve the output of functional chips, thereby enhancing profitability.

Examples & Applications

An example of scan chain insertion could be a simple chip that implements a basic logic function, requiring additional flip-flops to test each output signal effectively.

BIST in embedded systems allows a chip such as a mobile module to perform self-checks without external test equipment.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

DFT and BIST make testing fast, catch those faults, they’re built to last!

Stories

Imagine a smart assistant embedded in a chip that constantly checks its own functions. This is like BIST, ensuring everything runs smoothly.

Memory Tools

Remember DFT techniques with 'SBBAC': Scan chains, BIST, Boundary scan, At-speed testing, and Fault simulation.

Acronyms

To remember boundary scan, think of 'JTAG' - Joint Testing for Automated Gadgets.

Flash Cards

Glossary

- Design for Testability (DFT)

A set of techniques aimed at making testing of chips easier and more cost-effective.

- Scan Chain Insertion

A technique that adds flip-flops to allow access to internal chip signals for testing.

- BuiltIn SelfTest (BIST)

A method that embeds test logic in a chip that enables it to conduct self-testing.

- Boundary Scan (JTAG)

A testing standard that allows the checking of interconnects between chips.

- AtSpeed Testing

Evaluating a chip’s performance at operational clock speed to identify timing issues.

- Fault Simulation

Simulating various design faults to assess the effectiveness of testing strategies.

Reference links

Supplementary resources to enhance your learning experience.