Challenges in DFT and DFM

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Complexity of SoC Designs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to explore the challenges we face with Design for Testability and Design for Manufacturability. Let's start with the complexity of SoC designs. What do you think this means for our designs?

I think it means there are more components to manage. Does that complicate testing?

Exactly! The more components there are, the more intricate the interactions become. This can lead to a need for more sophisticated testing methodologies to ensure everything works correctly.

Could you give us an example of these sophisticated tools?

Sure! For instance, automated test pattern generation tools help generate test patterns that are essential for thorough testing. Remember, more complexity can often lead to more potential failure points.

So, is keeping SoC designs simpler the solution?

Not necessarily. Simplifying can compromise functionality or performance. The goal is to find a balance.

In summary, complex SoC designs require advanced tools and careful balancing to manage testability and manufacturability effectively.

Balancing Performance and Manufacturability

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s dive into the challenge of balancing performance optimizations with manufacturability. Why do you think this is important?

I guess if we focus too much on performance, it might make the chip harder to manufacture.

Correct! Advanced designs like FinFETs enhance performance but also introduce unique challenges. What do you think some of those challenges might be?

Maybe the manufacturing process needs to be adjusted for these designs?

Absolutely! Adjustments can lead to higher costs and longer production times if not managed properly. Balancing these factors is essential.

So, should we prioritize one over the other?

Ideally, we should strive for a design that meets both high performance and manufacturability standards. It's a difficult balance but crucial for industry competitiveness.

In conclusion, balancing these aspects is fundamental to successful VLSI design and can heavily influence production outcomes.

Ensuring Adequate Fault Coverage

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s talk about ensuring adequate fault coverage through DFT techniques. Why is this a challenging task?

Because we have to cover many scenarios while keeping within design constraints?

Exactly! It’s critical to identify as many faults as possible while adhering to physical constraints. Can anyone think of a situation where this balance might be tested?

What if a new technique comes out that could identify more faults but conflicts with the design?

Great point! New techniques that improve fault coverage may introduce complexities or constraints that make manufacturing harder. It’s an ongoing challenge.

So, what’s the best way to approach this challenge?

The best approach is to iteratively assess fault coverage in the design phases and keep an open dialogue between design and manufacturing teams.

In summary, ensuring adequate fault coverage is essential, and it's a continuous balancing act between identifying faults and maintaining design integrity.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The key challenges in DFT and DFM implementations include the increasing complexity of System on Chip (SoC) designs, the need to balance performance and manufacturability, and ensuring adequate fault coverage. Addressing these challenges is essential for optimizing chip production and maintaining high standards in design.

Detailed

In the realm of VLSI design, Design for Testability (DFT) and Design for Manufacturability (DFM) are pivotal for producing efficient and reliable chips. However, several challenges arise in effectively applying these principles:

- Complexity of SoC Designs: As System on Chip (SoC) designs become increasingly intricate, the need for sophisticated tools and methodologies to ensure testability and manufacturability grows.

- Balancing Performance and Manufacturability: Designers face the challenge of reconciling performance-enhancing optimizations with manufacturability requirements, particularly when working with cutting-edge technologies such as FinFETs or 3D ICs.

- Ensuring Adequate Fault Coverage: It is crucial to achieve high fault coverage through DFT techniques while also adhering to the physical constraints imposed by the design. This balance is essential for catching defects early and maintaining production efficiency.

Recognizing and addressing these challenges is critical for ensuring that semiconductor products meet the rigors of modern production demands.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Complexity of SoC Designs

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

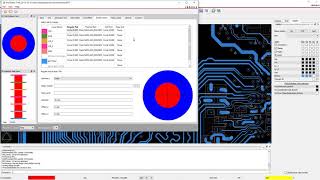

Despite the advancements in DFT and DFM techniques, several challenges remain:

- Complexity of SoC Designs: As designs become more complex, ensuring both testability and manufacturability requires sophisticated tools and methodologies.

Detailed Explanation

The complexity of System on Chip (SoC) designs refers to the intricate interconnections and functionalities that modern chips possess. As these designs grow, managing their testability – the ability to easily test them for defects – and manufacturability – the capacity to allow for efficient and flawless production – becomes increasingly difficult. Designers now need to utilize advanced software tools and methods to tackle this complexity effectively, which can be a significant challenge.

Examples & Analogies

Think of designing a modern smartphone. It includes various components like a camera, processor, and battery all integrated into a small space. If one part isn’t functioning well or is hard to test, it can impact the entire device’s performance. Similarly, in SoC designs, if the complexity isn't managed properly, the entire chip can face issues during testing and production.

Balancing Performance and Manufacturability

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Balancing Performance and Manufacturability: Designers need to balance performance optimizations with manufacturability requirements, especially when working with advanced technologies like FinFETs or 3D ICs.

Detailed Explanation

Balancing performance and manufacturability means that while engineers want their designs to operate as fast and effectively as possible, they also need to ensure that these designs can be made using existing manufacturing processes without incurring significant costs or complications. Advanced technologies like FinFET (Fin Field-Effect Transistor) and 3D ICs (integrated circuits) enable better performance but often require more precise manufacturing techniques that can complicate production.

Examples & Analogies

Imagine a high-speed car that has cutting-edge technology but is challenging to build on a production line. If the factory isn’t set up to make this car efficiently, they will either face delays, increased costs, or production errors. In the same way, chip designers must ensure that the advanced features in their designs can actually be manufactured without causing delays or defects.

Ensuring Adequate Fault Coverage

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Ensuring Adequate Fault Coverage: Achieving high fault coverage with DFT techniques while also considering the physical constraints of the design is a challenging task.

Detailed Explanation

Fault coverage refers to the ability of testing techniques to identify and ensure the proper functioning of all potential defects in the chip design. The challenge arises because designers must implement DFT techniques that account for various constraints, like the space available on the chip and the complexity of its circuitry. Striking a balance between achieving high fault coverage and working within these physical limitations can make testing difficult.

Examples & Analogies

Consider a security system for a house. To make sure that every entry point is secure, you might need a lot of sensors. However, if your home layout is very complicated, fitting all those sensors effectively becomes hard. Similarly, achieving comprehensive fault coverage in chip design requires balancing thorough testing with the design's physical and technical constraints.

Key Concepts

-

Complexity of SoC Designs: Refers to the intricate nature of modern chip designs that complicate DFT and DFM processes.

-

Balancing Performance and Manufacturability: The challenge of creating designs that perform well while being easy to manufacture.

-

Ensuring Adequate Fault Coverage: The difficulty in achieving fault coverage without violating physical design constraints.

Examples & Applications

An example of the complexity of SoC designs is the integration of multiple processing cores which requires advanced DFT tools to effectively test each core.

The challenge of balancing performance and manufacturability can be represented by the use of FinFET technology that enhances chip speed but complicates the fabrication process.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

DFT helps find a flaw, make sure your chips pass the law.

Stories

Imagine a bustling factory floor where chips are tested for faults. The workers are keen on finding every mistake to ensure smooth functioning, making sure each design meets manufacturability standards!

Memory Tools

Remember DFT as: Detecting Flaws Thoroughly.

Acronyms

Use the acronym BPF - Balance Performance with Fault coverage, for a successful design.

Flash Cards

Glossary

- DFT

Design for Testability - techniques to simplify testing of chips.

- DFM

Design for Manufacturability - strategies to optimize designs for manufacturing processes.

- SoC

System on Chip - integration of multiple components into a single chip.

- FinFET

Fin Field-Effect Transistor - a type of transistor used to improve performance in chips.

- Fault Coverage

The percentage of faults that can be detected during testing.

Reference links

Supplementary resources to enhance your learning experience.