Integration of DFT and DFM in VLSI Design

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Concurrent Consideration of DFT and DFM

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we’re talking about the integration of Design for Testability, or DFT, with Design for Manufacturability, or DFM. Why do you think it’s important to consider these two aspects simultaneously?

Because they both affect how well the chip functions and how easy it is to produce?

Exactly! Integrating DFT and DFM prevents complications later in the design process. Can you think of a specific scenario where delaying consideration of one might hurt the other?

If we add testability features late in the design, those could interfere with manufacturability, right?

Absolutely correct! That's why we aim for a balanced approach from the start. Let’s delve more into what that looks like in practice.

DFT and Layout Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s discuss layout optimization. When we optimize a design for testability, what considerations should we keep in mind for manufacturability?

We need to make sure that we don’t exceed the manufacturing rules like minimum spacing or feature sizes.

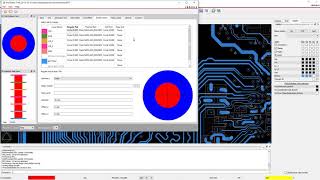

Correct! Using the term DRC, which stands for Design Rule Checking, can help us ensure we maintain those manufacturing rules while optimizing for testability.

How do we verify that our testability measures don’t interfere with the DRC?

Good question! We use software simulations to check compliance continually during the design process. This way, potential issues can be addressed before physical fabrication. Remember, early detection is key!

Manufacturing-Aware Testing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s talk about manufacturing-aware testing. Why do we need to apply DFM principles to testing?

To make sure that adding more test features doesn’t complicate the manufacturing process?

Exactly! We need to ensure that those test structures, such as scan chains or BIST, don’t violate manufacturing processes. Can you give an example of a potential conflict?

If we add too many flip-flops for scan chains, it could increase the chip's area and lead to fabrication issues?

Spot on! Balancing these aspects is crucial to avoid defects. It’s a classic case of balancing testability with manufacturability!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, the significance of integrating Design for Testability (DFT) and Design for Manufacturability (DFM) is highlighted, emphasizing how both principles work together during the VLSI design process to ensure chips are easy to test and manufacture while meeting quality standards. The discussion includes practical applications like layout optimization and manufacturing-aware testing to balance performance and manufacturability.

Detailed

Integration of DFT and DFM in VLSI Design

Design for Testability (DFT) and Design for Manufacturability (DFM) are two critical design principles in the world of Very Large Scale Integration (VLSI). Their integration during the design process is essential for ensuring that chips are both easily testable and manufacturable, aligning with the overall goals of the design team.

Key Points:

- Concurrent Consideration: Implementing DFT and DFM concurrently during the design process is crucial.

- DFT and Layout Optimization: While optimizing a chip’s layout for testability, designers must ensure the layout remains compliant with manufacturing rules, avoiding violations that could hinder the fabrication process.

- Manufacturing-Aware Testing: It is important to incorporate DFM principles to maintain the testability of designs, especially when applying DFT techniques like scan chains and Built-In Self-Test (BIST). This ensures that the addition of test features does not compromise the manufacturability of the design.

Understanding how to integrate these two principles effectively can lead to high-quality, functional chips with better yields and lower production costs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of DFT and DFM Integration

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Both DFT and DFM are integrated into the design process to ensure that the final chip meets both testability and manufacturability requirements. DFT focuses on ensuring that the chip can be effectively tested for functionality, while DFM ensures that the chip can be produced efficiently and reliably.

Detailed Explanation

In this part, we understand that Design for Testability (DFT) and Design for Manufacturability (DFM) work together during the chip design process. DFT aims to make sure that once the chip is manufactured, it can be tested for errors. On the other hand, DFM focuses on making the chip easy and cost-effective to produce without any issues. By combining these two principles, designers can create chips that not only perform well but are also less expensive and easier to produce.

Examples & Analogies

Think of building a bridge. DFT is like ensuring you have all the safety checks in place to make sure it holds up under traffic, while DFM is like making sure you have the right materials and construction methods so that building the bridge is not too costly and can be done efficiently. When both aspects are considered, the bridge will be safe and economical.

Concurrent Consideration in Design Process

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

During the design process, DFT and DFM should be considered concurrently. For example:

- DFT and Layout Optimization: While optimizing for testability, designers also need to ensure that the layout can be easily fabricated and does not violate design rules.

- Manufacturing-Aware Testing: DFM principles are applied to ensure that the testability of the design is not compromised, particularly when implementing scan chains, BIST, and other DFT techniques.

Detailed Explanation

This chunk emphasizes the importance of considering both DFT and DFM together during the chip design. It makes it clear that as designers work on making the chip easier to test (DFT) through methods like scan chains or Built-In Self-Test (BIST), they also need to keep in mind how these modifications will affect the manufacturing process (DFM). For instance, while creating test features, designers must avoid making the chip harder to produce or violating any design rules, which could lead to production problems.

Examples & Analogies

Imagine you're designing a new smartphone. DFT is like ensuring that the phone can be easily checked for software bugs before it hits the market, while DFM is figuring out how to mass-produce that phone without it costing a fortune. Just like a chef needs to follow a recipe that allows for both tasty food (good testing) and efficient cooking (easy manufacturing), chip designers need a balanced approach that satisfies both DFT and DFM.

Key Concepts

-

Integration of DFT and DFM: The need to implement both DFT and DFM principles simultaneously in chip design to ensure efficiency and quality.

-

Layout Optimization: Adjusting the design layout to enhance testability while adhering to manufacturing constraints.

-

Manufacturing-Aware Testing: The application of DFM strategies to maintain testability during the implementation of DFT techniques.

Examples & Applications

When designing a chip, the integration of DFT and DFM may involve running simulations to ensure that adding test structures does not lead to layout violations.

A practical example of manufacturing-aware testing is implementing scan chains without exceeding the boundaries defined by the DRC.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Test for a chip, don’t let it trip. Design it right, give DFM a light.

Stories

Once upon a time, there were two friends, DFT and DFM, who worked together in a design studio. They realized that if they focused only on one aspect, their design projects would fall short, but together, they created designs that were both testable and manufacturable.

Memory Tools

Remember DFT as 'Designing Functionality Tests' to focus on testing strategies.

Acronyms

Let DFM remind you of 'Design for Max yield' indicating its importance in manufacturability.

Flash Cards

Glossary

- Design Rule Checking (DRC)

A verification process that ensures a design adheres to certain manufacturing constraints and rules to avoid defects.

- Design for Testability (DFT)

A set of techniques intended to make testing easier and more efficient during the chip design and production process.

- Design for Manufacturability (DFM)

A series of principles applied during design to ensure a product can be manufactured efficiently and reliably.

- Scan Chain

A chain of flip-flops that allows for examination of internal chip states to facilitate testing.

Reference links

Supplementary resources to enhance your learning experience.