Algorithms for Timing Optimization

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Static Timing Analysis (STA)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we'll start our discussion on timing optimization with Static Timing Analysis, or STA. Can anyone tell me why analyzing timing is crucial in circuit design?

Isn’t it important to ensure that signals propagate correctly?

Exactly! STA checks the timing without simulation by finding paths that exceed timing constraints. It checks for setup and hold violations. Why do you think this is better than running circuit simulations?

Maybe because it's faster? We don't have to run the entire circuit through a simulation?

Right! STA can quickly analyze multiple paths. Remember this acronym, STA: Speedy Timing Analysis. Now, can anyone share ways violation can affect circuit performance?

If signals don’t settle before the next clock edge, it might cause incorrect operations.

Correct! That’s why STA is essential. It helps find issues upfront. Any final thoughts on STA before moving on?

It's a proactive way to catch timing issues!

Great summary! Let's dive deeper into another technique - Retiming.

Retiming

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we're discussing Retiming, which is about rearranging flip-flops to optimize timing. What do you think is the main goal of this technique?

To reduce the critical path, so the clock can run faster?

That's right! By moving flip-flops around, we can decrease delays. Retiming doesn’t change functionality but improves speed. Can anyone explain how we might determine where to move a flip-flop?

Maybe by checking which paths are slowest and then adjusting flip-flops?

Exactly! We focus on critical paths. Let’s remember: Retiming = Rearranging for speed. What questions do you have about how this is conducted in practice?

Do we use any algorithms to do this?

Yes! Various algorithms help automate this process. Let’s move on to our next strategy—Logic Duplication.

Logic Duplication

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's discuss Logic Duplication. What do you think might be the rationale behind duplicating logic elements in a circuit?

To speed up computation along the critical paths!

Correct! By duplicating logic, we can mitigate the delay on paths critical for performance. Why would this be advantageous in large-scale designs?

It helps in balancing the loads and improving timing without affecting overall design.

Exactly! But remember, duplication can also increase area and power. So, balance is key. Can anyone summarize why balancing timing is crucial?

To ensure that all parts of the circuit function in harmony, meeting the timing requirements.

Great summary! Remember: Logic Duplication = Speed on critical paths but keep an eye on area/power trade-offs. Any questions before we wrap up?

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, various timing optimization algorithms are explored, including Static Timing Analysis (STA), Retiming, and Logic Duplication. These techniques are essential for ensuring that circuits meet critical timing requirements.

Detailed

Algorithms for Timing Optimization

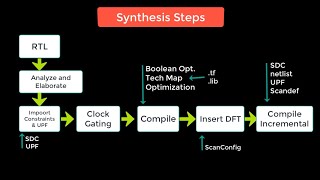

Timing optimization is crucial in VLSI design to ensure that the synthesized circuit operates within specified timing constraints. Several techniques serve this purpose:

- Static Timing Analysis (STA): STA is a methodology for checking the timing of a circuit without simulation. It rigorously analyses different paths in the circuit to ensure that they do not violate timing constraints, such as setup and hold violations. STA guarantees that any timing-related issues can be identified early in the design cycle.

- Retiming: This technique involves repositioning flip-flops to enhance circuit timing without altering its functionality. By shifting flip-flops along the data paths, retiming can decrease the critical path length, thus enabling a higher clock frequency and improved performance.

- Logic Duplication: This technique aims to speed up critical paths by duplicating certain logic elements. The duplication helps reduce the delay along specific pathways, thus balancing the overall timing of the circuit.

These algorithms play a vital role in the timing optimization process of VLSI design, ensuring that the synthesized circuits can function correctly while maximizing performance efficiency.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Timing Optimization

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing optimization ensures that the synthesized circuit operates within the required timing constraints. Several timing-related synthesis techniques are used to guarantee that the design meets the performance specifications.

Detailed Explanation

Timing optimization is critical in ensuring that electronic circuits perform their intended functions at the right speed. If a circuit cannot meet its timing constraints, it may malfunction. So, timing optimization techniques help to adjust circuit parameters carefully to meet these specific speed requirements.

Examples & Analogies

Imagine you're trying to coordinate multiple tasks to meet a deadline, like organizing a school event. If one part of the event (like food delivery) is delayed, it can disrupt the entire schedule. Similarly, in circuits, if one operation takes too long, it can delay the entire function of the circuit.

Static Timing Analysis (STA)

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Static Timing Analysis (STA): STA is used to analyze the timing of a circuit without requiring simulation. It checks whether any paths in the design violate the timing constraints (e.g., setup and hold violations).

Detailed Explanation

Static Timing Analysis (STA) is a method that engineers use to verify that a circuit's timing is reliable. This technique examines every possible timing path within a circuit without needing to simulate the entire circuit's operation. It helps identify and resolve issues where signals may not arrive at their destinations quickly enough (setup violations) or where signals may disturb each other (hold violations).

Examples & Analogies

Think of STA like a train schedule. Inspecting the schedule lets you check if trains arrive and depart on time without needing to watch every train. If a train is consistently late (setup violation), it may disrupt connections (timing paths) with other services.

Retiming

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Retiming: This technique involves shifting flip-flops in the circuit to optimize the timing of the design without changing its functionality. It can help reduce the critical path and improve clock frequency.

Detailed Explanation

Retiming is a strategic method used to rearrange flip-flops, which are memory elements in digital circuits. By moving these elements around, designers can optimize timing and make the circuit faster, all without altering what the circuit does. This adjustment helps to make sure that signals travel through the circuit in the shortest time possible.

Examples & Analogies

Imagine rearranging furniture in a room to create a clearer pathway for people to walk through. While you haven’t changed the room’s purpose, you’ve made it easier to navigate. Similarly, retiming allows the circuit to function more efficiently by improving signal flow.

Logic Duplication

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Logic Duplication: Logic duplication involves duplicating certain logic elements to speed up critical paths. This helps to balance the circuit’s timing by reducing the delay of specific paths.

Detailed Explanation

Logic duplication is a technique where specific logic components in a circuit are duplicated to enhance timing performance. This duplication helps reduce delays along critical paths, or the longest sequence of operations that a signal has to traverse, ensuring the circuit functions efficiently and meets its speed requirements.

Examples & Analogies

Consider a relay race where one runner is much slower than the others and affects the overall performance of the team. By adding another runner to help share the load (logic duplication), the team's overall speed can increase, preventing the slowest part from dragging down the entire relay.

Key Concepts

-

Static Timing Analysis: Analyzes circuit paths to ensure timing constraints are met.

-

Retiming: Rearranges flip-flops to enhance performance without altering functionality.

-

Logic Duplication: Speeds up critical paths by duplicating logic elements.

Examples & Applications

Example of STA: A circuit with two paths where STA reveals that one path has a timing violation, leading to redesign.

Example of Retiming: Moving a flip-flop from one location to another within a circuit to reduce the critical path length.

Logic Duplication Example: Duplicating a logic gate along a critical delay path to allow faster computations along that path.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

STA helps check the race, ensuring circuits stay in pace.

Stories

Imagine a chef timing when to add spices to a stew. If he adds too soon, it's ruined. STA helps ensure spices are timely added, just like signals must settle in circuits.

Memory Tools

Remember the acronym RLP: Retiming, Logic Duplication, Performance - all aimed at improving circuit timing!

Acronyms

STA

Save Time Analyzing - to keep our timing in check!

Flash Cards

Glossary

- Static Timing Analysis (STA)

A method to analyze the timing of a circuit without simulation to find timing violations.

- Retiming

The process of moving flip-flops within a circuit to improve timing without changing functionality.

- Logic Duplication

A technique where certain logic elements are duplicated to reduce delays in critical paths.

Reference links

Supplementary resources to enhance your learning experience.