Introduction to Logic Synthesis in VLSI Design

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Overview of Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we are going to discuss the concept of logic synthesis. Which of you can tell me what logic synthesis is?

Is it the process of converting high-level descriptions into something that can be implemented in silicon?

Exactly! Logic synthesis is the process that transforms high-level functional descriptions, such as those written in VHDL or Verilog, into a gate-level representation. This conversion is crucial as it optimizes the design for area, power, and performance.

What is meant by optimizing for area, power, and performance?

Great question! Optimizing for area means minimizing the physical space the circuit occupies, while power optimization involves reducing the energy consumption. Performance optimization looks at improving circuit speed.

So, is the synthesized logic just a network of gates?

Yes, that's correct! After synthesis, your design will be represented as a network of logic gates, ultimately enabling its physical implementation.

To summarize, logic synthesis is vital in VLSI design as it translates high-level descriptions into optimized gate-level representations, laying the foundation for efficient designs.

Goals of Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive deeper into the main goals of logic synthesis. What do you think these could be?

I believe it should aim to make the design more compact and faster?

Exactly! The primary goals of logic synthesis involve optimizing area, power, and performance. Would anyone like to elaborate on why these factors are crucial?

Compact designs are essential as chips get more complex; otherwise, it would lead to higher costs and power consumption.

Right! Compact designs not only save space but also often lower costs and improve efficiency by reducing power use. Performance-wise, faster circuits can handle more complex tasks efficiently.

So, optimizing all these factors makes the design more effective in real-world applications?

Absolutely! In summary, the goals of logic synthesis focus on enhancing circuit efficiency and effectiveness, making it critical in the design process.

Importance of Algorithms in Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s talk about the algorithms used in logic synthesis. Why do we need these algorithms?

I suppose the algorithms help automate the conversion from high-level descriptions to gate-level representations?

Exactly! Logic synthesis relies on various algorithms to efficiently perform this conversion while ensuring optimization. What do you think could happen without these algorithms?

It would be a lot more time-consuming and possibly lead to errors!

Yes, without these algorithms, the design process would not only be labor-intensive but also prone to errors, which would compromise performance and efficiency. Algorithms help streamline the process, allowing for accurate and reliable synthesis.

In summary, algorithms are the backbone of logic synthesis, automating complex tasks to ensure optimized and error-free circuit designs.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

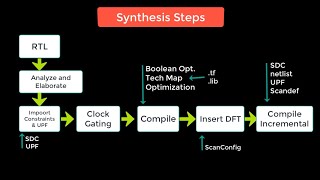

In VLSI design, logic synthesis is essential for converting high-level descriptions specified in hardware description languages into gate-level implementations. It focuses on optimizing the design for area, power, and performance through various methods, ultimately forming the foundation for the core algorithms explored throughout the chapter.

Detailed

Introduction to Logic Synthesis in VLSI Design

Logic synthesis serves as a pivotal step in the VLSI design process, effectively bridging high-level functional descriptions—written in hardware description languages such as VHDL and Verilog—with gate-level representations that can be physically implemented. The core goal of this transformation is to optimize design concerning three critical factors: area, power, and performance.

This chapter aims to delve into the fundamental algorithms that underpin logic synthesis, scrutinizing the various methodologies as well as their benefits and drawbacks in practical applications. By systematically converting behavioral or structural circuit descriptions into networks of logic gates, logic synthesis lays the groundwork for subsequent stages of design and realization in VLSI technology.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

What is Logic Synthesis?

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Logic synthesis is a crucial step in the VLSI design process, where high-level functional descriptions (usually in hardware description languages like VHDL or Verilog) are transformed into a gate-level representation suitable for physical implementation.

Detailed Explanation

Logic synthesis is the process of converting the high-level design of a digital circuit into a format that can be implemented physically. Designers write circuit descriptions in specialized languages (like VHDL or Verilog), which describe how the circuit should behave. Logic synthesis takes this high-level description and changes it into a series of logic gates (AND, OR, NOT, etc.) that can actually be built in silicon.

Examples & Analogies

Think of logic synthesis like translating a recipe written in a detailed book (the high-level description) into actual cooking steps (the gate-level representation). Just as a cook transforms ingredients into a dish by following specific steps, logic synthesis translates the design into a form that can be manufactured as an electronic circuit.

Goals of Logic Synthesis

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The main goal of logic synthesis is to optimize the design in terms of area, power, and performance.

Detailed Explanation

When synthesizing logic, designers aim to achieve three main objectives: minimizing the area (how much space the circuit occupies), reducing power consumption (how much energy the circuit uses), and maximizing performance (how quickly the circuit operates). This optimization is critical because it ensures the circuit meets specified requirements while remaining efficient and effective.

Examples & Analogies

Imagine a city planner trying to design a new neighborhood. The planner wants to build houses that fit in small plots (area), keep construction costs low (power), and ensure that residents can travel quickly between places (performance). Each concept is important for the overall functionality and livability of the neighborhood, just like area, power, and performance are crucial in circuit design.

Process of Logic Synthesis

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This process involves translating the behavioral or structural description of the circuit into a network of logic gates.

Detailed Explanation

The synthesis process begins by taking the initial behavioral or structural description provided at the high level and interpreting that into a specific arrangement of logic gates. This step ensures that the logical operations described by the designer can be physically realized and interconnected to perform the desired tasks.

Examples & Analogies

Consider building a model from a set of instructions. The initial description may tell you how the final model should function (its behavior), while the synthesis process is like deciding which pieces to use and how to connect them (the structural description) to build the model correctly. It’s the step-by-step process of bringing plans to existence.

Core Algorithms in Logic Synthesis

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this chapter, we will focus on the core algorithms used in logic synthesis, examining their approaches, advantages, and limitations.

Detailed Explanation

Logic synthesis relies on various algorithms to automate the conversion of high-level descriptions to gate-level implementations. Each algorithm has specific techniques that help optimize different aspects of the design. This chapter will cover these algorithms in detail, looking at how they work, what benefits they offer, and where their limitations might lie.

Examples & Analogies

Think of different cooking techniques (like frying, baking, steaming) that can be used for various recipes. Each technique has its pros and cons depending on the dish being prepared. Similarly, different algorithms in logic synthesis are like these techniques—they are tailored to specific design tasks and can lead to different outcomes based on their use.

Key Concepts

-

Logic Synthesis: The process of converting high-level functional descriptions into gate-level representations.

-

VLSI Design: Integration of thousands or millions of transistors on a single chip.

-

Optimization: Minimizing area, power, and performance in circuit design.

Examples & Applications

Using VHDL to describe a new circuit and applying logic synthesis to derive its gate-level implementation.

An example of optimizing a design by reducing the number of gates used while ensuring that the performance requirements are met.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

From HDL to gates, watch the change, optimizing design, nothing feels strange.

Stories

Imagine a farmer deciding how to plant crops (Area), how much water to use (Power), and how to make the crops grow quickly (Performance). Just like the farmer, logic synthesis balances these three needs for a successful yield!

Memory Tools

Remember A-P-P for Area, Power, and Performance—these are the key goals of logic synthesis.

Acronyms

S.O.P. stands for Synthesis, Optimization, Performance—a reminder of the essential tasks of logic synthesis.

Flash Cards

Glossary

- Logic Synthesis

The process of converting high-level functional descriptions into gate-level representations in VLSI design.

- VLSI

Very-Large-Scale Integration; a method of creating integrated circuits by combining thousands or millions of transistors onto a single chip.

- Hardware Description Language (HDL)

A specialized programming language used to describe the behavior and structure of electronic systems.

- GateLevel Representation

A realization of a design in terms of logic gates rather than its original functional description.

- Optimization

The process of making a design as effective, functional, and efficient as possible.

Reference links

Supplementary resources to enhance your learning experience.