Conclusion

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Overview of Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, let's recapture the essence of logic synthesis. Can anyone tell me what logic synthesis is?

Isn't it the process of converting high-level descriptions into gate-level representations?

Exactly! And why is this transformation important in VLSI design?

To optimize designs for performance, area, and power consumption!

Spot on! Remember, we use various algorithms to achieve this. For example, can anyone name one of the algorithms we discussed?

The Espresso algorithm for Boolean minimization!

Great! The Espresso algorithm helps simplify Boolean functions effectively, aiding in overall optimization. Can someone explain its significance?

It makes circuits smaller and faster by reducing unnecessary complexities!

Yes! Well said. In summary, logic synthesis algorithms, like Espresso, are crucial for efficient VLSI designs.

Technology Mapping

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's talk about technology mapping. Who can explain what technology mapping involves?

It's about mapping synthesized Boolean functions to actual gates from technology libraries!

Correct! This step is essential for ensuring our design can be physically implemented. What are the two types of mapping we discussed?

Cell-based mapping and technology-independent mapping!

Exactly! Can anyone give me a brief difference between the two?

Cell-based mapping directly uses available cells, whereas technology-independent mapping first optimizes without specific gates.

Well explained! Remember, effective technology mapping is crucial for meeting area and performance requirements.

Power Optimization Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive into power optimization in VLSI design. Who remembers one technique for reducing power?

Clock gating!

Yes! Clock gating turns off the clock to parts of a circuit when not in use, reducing dynamic power. Why is that significant?

It greatly lowers the power consumption in large designs!

Exactly! Additionally, gate-level power optimization techniques are also important. Can someone give an example?

They minimize the switching activity of gates to reduce power usage!

Correct! Efficient power consumption is becoming more critical as circuit complexity rises. In summary, understanding these techniques is key to creating modern VLSI designs.

Importance of Timing Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s discuss timing optimization. Why do we need timing optimization in logic synthesis?

To ensure that the circuit meets specified timing constraints!

Exactly! What are some techniques related to timing optimization we learned?

Static Timing Analysis, retiming, and logic duplication!

Perfect! Let’s focus on retiming for a moment. What does it involve?

Shifting flip-flops in the circuit to optimize timing without changing functionality.

Well said! Remember, every timing optimization technique we discussed plays a vital role in enhancing circuit performance.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

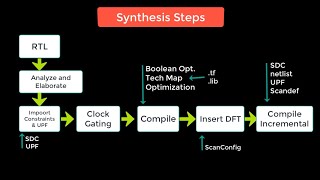

In the conclusion of chapter 3, we synthesize the key algorithms related to logic synthesis in VLSI design. We discuss the importance of these algorithms, including Boolean minimization, technology mapping, and optimization techniques, while noting their significance as VLSI designs grow in complexity.

Detailed

Conclusion

In this chapter, we have delved into the essential logic synthesis algorithms that form the backbone of modern VLSI design. Logic synthesis involves translating high-level functional descriptions into gate-level representations that are optimized for area, power, and performance. Key algorithms discussed include Boolean minimization techniques such as the Espresso algorithm, methods for technology mapping, timing optimization strategies, and considerations for sequential synthesis. Each of these algorithms plays a critical role in efficiently transforming designs into manufacturable circuits. As the scale and complexity of VLSI designs continue to increase, the importance of efficient synthesis algorithms becomes even more critical. In the following chapters, we will explore these algorithms further and see their application in industry-standard VLSI design tools.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of Logic Synthesis Algorithms

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this chapter, we have delved into the essential logic synthesis algorithms that form the backbone of modern VLSI design.

Detailed Explanation

This section summarizes the main focus of the chapter, which is on the critical algorithms used for logic synthesis in Very Large Scale Integration (VLSI) design. It emphasizes that these algorithms are foundational for creating designs that are both functional and efficient.

Examples & Analogies

Think of these algorithms like the skilled cooks in a kitchen, working together to turn raw ingredients (the high-level design) into a gourmet meal (the final circuit) that is ready for serving (manufacturing). Each cook has a specific role, just as each algorithm has its unique purpose in the design process.

The Importance of Efficient Synthesis Algorithms

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As the scale and complexity of VLSI designs continue to increase, the importance of efficient synthesis algorithms becomes even more critical.

Detailed Explanation

This chunk explains that as technology progresses, VLSI designs are becoming more intricate. Consequently, it is increasingly vital to have efficient algorithms that can handle these complexities while ensuring that the designs remain optimally functional and manufacturable.

Examples & Analogies

Imagine a city planner who must design a new urban area. As the population grows and the city expands, the planner needs better strategies (or algorithms) to design roads, parks, and buildings that are effective and sustainable, much like synthesis algorithms help engineers manage complex circuit designs efficiently.

Future Exploration of Algorithms

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In the following chapters, we will explore these algorithms further and see their application in industry-standard VLSI design tools.

Detailed Explanation

This final chunk indicates that the upcoming chapters will provide deeper insights into the discussed algorithms and how they are applied in real-world VLSI design tools. This transition hints at practical applications of the theoretical knowledge presented in the chapter.

Examples & Analogies

Just like in a mystery novel where the plot thickens with more layers to uncover, the next chapters promise to reveal more complex and fascinating uses of these algorithms that readers will find useful in understanding modern technology.

Key Concepts

-

Logic Synthesis: The process of converting high-level functional descriptions into gate-level representations.

-

Boolean Minimization: Techniques to simplify Boolean expressions for optimizing digital circuits.

-

Technology Mapping: Mapping synthesized logic to actual gates in a technology library.

-

Timing Optimization: Ensuring the circuit meets defined timing constraints.

Examples & Applications

The Espresso algorithm significantly reduces the complexity of Boolean functions, aiding in smaller and faster designs.

Using clock gating can drop power consumption to nearly half in certain complex VLSI designs.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When designing chips, keep it tight, Use Espresso right for circuits light!

Stories

Imagine an engineer named Lisa, who was struggling with her circuit design. After using Boolean minimization through the Espresso algorithm, she found her design much simpler and faster!

Memory Tools

Remember 'BTT' for minimizing: Boolean, Timing, Technology.

Acronyms

Use 'OPT' to remember

Optimize

Power

Timing strategies in synthesis.

Flash Cards

Glossary

- Boolean Minimization

A process for simplifying Boolean expressions to reduce the complexity of digital circuits.

- Technology Mapping

The process of mapping synthesized logic functions to actual gates in a technology library.

- Static Timing Analysis (STA)

A technique used to analyze the timing of a circuit without requiring simulation.

- Retiming

Shifting flip-flops in a digital circuit to optimize timing.

Reference links

Supplementary resources to enhance your learning experience.