Key Concepts in Logic Synthesis

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Optimization in Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll start with Optimization in Logic Synthesis. The main goal is to minimize the number of gates and the circuit's size while still meeting performance requirements. Can anyone tell me why optimization is important in VLSI design?

Optimization reduces costs and improves performance, right?

Exactly! Also, can anyone remember a specific strategy we might use during optimization?

We could use Boolean simplification methods?

Yes, Boolean minimization techniques help simplify the functions. Also, remember 'OGPB' - Optimize Gates, Power, and Balance—helps us recall our goals in optimization. Why is balancing these elements important?

It ensures the design is effective across all performance metrics!

Great point! In optimizing, we want a design that performs well without extra costs or delays.

Technology Mapping

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's discuss technology mapping. This is where we map our synthesized logic to available gates in a technology library. Why do we need to do this?

To ensure the logic we create can be physically implemented using real components?

Exactly! This also allows us to optimize area and performance. Who can tell me the two types of mapping used?

Cell-Based Mapping and Technology-independent Mapping!

Correct! Cell-Based Mapping uses specific standard cells, while Technology-independent Mapping focuses first on optimizing logic before finding cell implementation. Why might technology-independent mapping be preferred in some cases?

It could lead to better optimization before focusing on physical limits?

Absolutely! A more abstract focus can yield better logical simplifications.

Boolean Minimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we must cover Boolean Minimization. Can anyone explain why minimizing Boolean functions is crucial?

It reduces complexity which can minimize area and delay in circuits!

Correct! Different algorithms like Quine-McCluskey, Karnaugh Maps, and Espresso are used for this process. Which one of these is exhaustive?

The Quine-McCluskey algorithm!

Exactly! It explores all combinations for simplification. Espresso is more practical in real applications, focusing on heuristic approaches. Remember the acronym 'QKE' — Quine, Karnaugh, Espresso?

That makes it easier to recall which algorithms do what!

Fantastic! Using these algorithms effectively can streamline our design process significantly.

RTL to Gate-Level Conversion

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's move to the RTL to Gate-Level conversion. This step is essential as we move from a high-level description to a form that can be practically implemented. What does RTL represent?

It focuses on the timing and control of the data flow!

Exactly! It abstracts the operations while defining how we manage registers, switching to gates starts with utilizing the available technology. Why do you think this step is necessary?

It’s about practical implementation—gate-level designs can be fabricated!

Great reasoning! Without this conversion, our designs would remain theoretical, not allowing us to create actual circuits.

Timing Analysis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, we'll look at Timing Analysis. Ensuring our designs meet specific timing constraints is vital for the circuit's functionality. What timing aspects should we consider?

Setup times, hold times, propagation delays, and clock skew!

Exactly right! Meeting these constraints is essential to avoid issues like mis-timed signals. Has anyone heard of Static Timing Analysis?

Yeah, it analyzes timing without needing to simulate it!

Correct! It provides a quick way to ensure all paths in the circuit meet requirements, helping us identify potential violations before they become problems. Always remember: 'TAP'—Timing Analysis is Paramount!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The key concepts in logic synthesis include optimization strategies to minimize circuit complexity, technology mapping to standard cells, Boolean minimization techniques, conversion from RTL to gate-level representations, and ensuring that timing constraints are met. Each of these tasks is vital for creating efficient VLSI circuits.

Detailed

Key Concepts in Logic Synthesis

Logic synthesis is a pivotal aspect of VLSI design, focusing on transforming functional descriptions into optimized gate-level representations. This section delineates five crucial tasks:

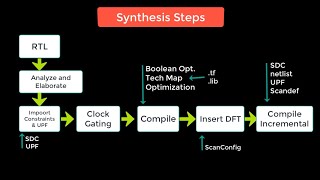

- Optimization: The goal is to minimize both the number of gates utilized and the overall size of the circuit, balancing performance needs.

- Technology Mapping: This process involves converting synthesized logic into specific gates from a selected technology library to achieve optimal designs.

- Boolean Minimization: Techniques are employed to reduce the complexity of Boolean functions, enabling simpler and more efficient circuit designs.

- Register Transfer Level (RTL) to Gate-Level Conversion: This involves translating RTL descriptions into specific gate-level representations that can be physically implemented.

- Timing Analysis: Critical to ensuring that timing constraints such as setup times and propagation delays are satisfied, guaranteeing that designs function correctly under operational conditions.

Understanding these tasks is vital for efficient VLSI design, forming the foundation for subsequent stages of synthesis algorithms that further enhance the circuit performance.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Optimization in Logic Synthesis

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Optimization: Minimizing the number of gates and the size of the circuit while meeting performance requirements.

Detailed Explanation

Optimization in logic synthesis refers to the process of reducing the overall complexity of a digital circuit. This can involve minimizing the number of gates, which are the basic building blocks of digital logic, and ensuring the circuit occupies minimal physical space on a chip. The goal is to balance performance metrics, such as speed, power consumption, and area (physical size). An optimized design is essential for efficient manufacturing of Integrated Circuits (ICs).

Examples & Analogies

Think of optimization like packing a suitcase for a trip. You want to fit as many necessary items as possible (functionality) without exceeding the weight limit (area/performance requirements). By carefully selecting items and organizing them efficiently, you can maximize your packing without overloading yourself.

Technology Mapping

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Technology Mapping: Mapping the synthesized logic to available standard cells (gates) from a given technology library.

Detailed Explanation

Technology mapping is the process of taking the optimized logic design generated during synthesis and translating it into actual logical gates available in a specific technology library (e.g., AND gates, OR gates, etc.). This ensures that the synthesized design can be physically manufactured using the available technology while adhering to constraints such as size and performance. It plays a critical role in the transition from abstract designs to tangible circuits.

Examples & Analogies

Think of technology mapping like selecting ingredients for a recipe based on what you have in your kitchen. If the recipe calls for specific types of produce, but you have only certain items on hand, you need to adapt the recipe using available ingredients to ensure the dish still turns out as intended.

Boolean Minimization

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Boolean Minimization: Reducing the complexity of the Boolean functions that represent the logic design.

Detailed Explanation

Boolean minimization is the process of simplifying Boolean expressions that describe the logic of a circuit. By reducing complexity, logic circuits can be made smaller and faster. This is achieved through various techniques, which aim to eliminate redundant operations and simplify the overall expression while maintaining the same functionality. Minimization is crucial for ensuring efficient circuit designs.

Examples & Analogies

Think about cleaning out a closet full of clothes. If you never wear certain items, they take up space and clutter. By removing those unnecessary pieces, you make it easier to find your favorite outfits in a well-organized closet, just like simplifying a Boolean function helps clarify the logic of a circuit.

Register Transfer Level (RTL) to Gate-Level Conversion

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Register Transfer Level (RTL) to Gate-Level: Converting RTL representations to gate-level representations.

Detailed Explanation

The conversion from Register Transfer Level (RTL) to Gate-Level involves taking a high-level abstraction of a digital system and translating it into specific gate-level designs. RTL descriptions outline the flow of data and the operations performed on this data, while gate-level representations show how these operations are implemented using logical gates. This transformation is essential for finalizing a design that can be synthesized into hardware.

Examples & Analogies

It's similar to creating a blueprint for a house (RTL) and then breaking that blueprint down into specific construction materials and processes (gate-level). The blueprint provides a high-level overview, while the construction details are necessary for building the actual house.

Timing Analysis

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Timing Analysis: Ensuring that the design meets timing constraints, such as setup and hold times, propagation delays, and clock skew.

Detailed Explanation

Timing analysis is a critical process in digital design that checks whether the circuit meets all time-based requirements for correct operation. Key timing parameters include setup time (the time required for inputs to be stable before a clock edge), hold time (the time inputs need to remain stable after a clock edge), propagation delay (the time it takes for a signal to travel through a gate), and clock skew (the difference in timing between signals in different parts of a circuit). Ensuring all timing requirements are met is essential for reliable circuit function.

Examples & Analogies

Consider timing analysis like coordinating a group of runners in a relay race. Each runner must start and finish their leg of the race at precise moments to ensure a smooth transition and avoid disqualification. Timing analysis ensures that all parts of the circuit function together seamlessly, like a well-coordinated relay team.

Key Concepts

-

Logic synthesis is a pivotal aspect of VLSI design, focusing on transforming functional descriptions into optimized gate-level representations. This section delineates five crucial tasks:

-

Optimization: The goal is to minimize both the number of gates utilized and the overall size of the circuit, balancing performance needs.

-

Technology Mapping: This process involves converting synthesized logic into specific gates from a selected technology library to achieve optimal designs.

-

Boolean Minimization: Techniques are employed to reduce the complexity of Boolean functions, enabling simpler and more efficient circuit designs.

-

Register Transfer Level (RTL) to Gate-Level Conversion: This involves translating RTL descriptions into specific gate-level representations that can be physically implemented.

-

Timing Analysis: Critical to ensuring that timing constraints such as setup times and propagation delays are satisfied, guaranteeing that designs function correctly under operational conditions.

-

Understanding these tasks is vital for efficient VLSI design, forming the foundation for subsequent stages of synthesis algorithms that further enhance the circuit performance.

Examples & Applications

In optimization, a circuit designed using fewer gates while maintaining performance can significantly reduce chip area and power consumption.

Technology mapping allows an AND gate synthesized logic to be mapped specifically to a single physical gate in a used technology library, improving performance.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To optimize your circuit’s grace, keep the gates in their best place.

Stories

Imagine walking through a complex maze (circuit). Each turn represents a choice to make (optimization). You can avoid dead ends (unused gates) by taking the right path (minimization) to reach your destination (functional circuit).

Memory Tools

Remember 'O-T-B-R-T': Optimize, Technology, Boolean, RTL, Timing!

Acronyms

Use 'TAP' for Timing Analysis

Timing

Analysis

Precision!

Flash Cards

Glossary

- Optimization

The process of minimizing gate usage and circuit size while meeting performance requirements.

- Technology Mapping

The mapping of synthesized logic to specific gates from a technology library.

- Boolean Minimization

Techniques used to reduce the complexity of Boolean functions.

- Register Transfer Level (RTL)

A high-level abstraction that describes the data flow and operations in terms of registers and transfer operatives.

- Timing Analysis

A method to ensure that a digital circuit meets its timing constraints.

Reference links

Supplementary resources to enhance your learning experience.