High-Level Synthesis (HLS)

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to High-Level Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're discussing High-Level Synthesis, or HLS. Can anyone tell me what HLS actually does in the context of VLSI design?

Isn't it about generating hardware from high-level programming languages?

Exactly! HLS automates the conversion of high-level languages like C or C++ into hardware architectures, greatly simplifying the design process. Why do you think this is important?

It must save a lot of time because writing RTL manually for complex circuits is really tedious.

That's right! It allows for quicker iterations and reduces the complexity of manual RTL creation, making it a powerful tool in modern VLSI design.

Scheduling in HLS

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's dive into scheduling in HLS. Why do you think an efficient scheduling algorithm is critical?

It probably determines the order of operations, right? If they're out of order, it could delay everything.

Good observation! Scheduling optimizes operational order to minimize delays and resource usage. It’s key to maximizing performance. Remember the acronym 'LEAP'—it stands for 'Learn, Execute, Arrange, Performance'—to help memorize the importance of scheduling in HLS.

Binding in HLS

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In HLS, binding assigns operations to hardware resources. Can anyone share why efficient binding is essential?

Maybe it helps minimize the usage of hardware resources like functional units?

Exactly! Effective binding minimizes resource utilization and optimizes power consumption, leading to efficient hardware design. Think of the mnemonic ‘RAMP’ to remember: 'Reduce, Assign, Minimize, Power'.

Advantages of HLS

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

What benefits do you think HLS provides in terms of design methodologies?

It speeds up the design process and allows for more flexibility with complex designs.

Correct! HLS accelerates the design time significantly and allows designers to make adjustments quickly to meet performance requirements, thus enhancing innovation.

HLS in Practice

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, how do you see HLS being implemented in real-world projects?

I imagine it's used in projects that require quick hardware development cycles, like for mobile devices or IoT applications.

Absolutely! HLS is invaluable in fields like IoT, where rapid development and performance are critical due to the rapidly changing technology landscape.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

High-Level Synthesis (HLS) automates the generation of hardware designs from high-level languages such as C or C++. It focuses on scheduling the order of operations and binding operations to hardware resources, aiming to enhance performance without manual RTL design.

Detailed

High-Level Synthesis (HLS)

High-Level Synthesis (HLS) represents a significant abstraction beyond traditional Register Transfer Level (RTL) synthesis methods. Instead of requiring designers to manually write RTL descriptions for complex circuits, HLS allows for the automation of hardware generation from higher-level programming languages such as C, C++, or SystemC. This automation is particularly beneficial for intricate designs that would be cumbersome to encode directly in RTL.

Key Concepts in HLS:

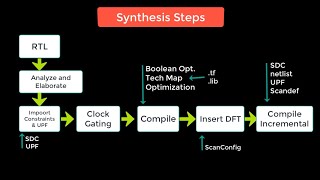

- Scheduling: HLS algorithms define the sequence in which various operations take place within a design. Proper scheduling is crucial for optimizing both time and resource consumption, ensuring that the generated hardware operates efficiently.

- Binding: This phase involves assigning specific hardware resources, such as functional units or memory elements, to the scheduled operations. Effective binding reduces resource utilization and enhances power efficiency, allowing the final hardware architecture to meet performance requirements.

HLS not only makes the design process more accessible but also enables rapid iterations and adjustments necessary for meeting performance metrics in modern VLSI systems. Overall, HLS generates efficient hardware implementations from complex high-level designs, decreasing the time-to-market for new technologies.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to High-Level Synthesis (HLS)

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

High-Level Synthesis is an abstraction above traditional RTL synthesis. HLS algorithms automate the process of generating hardware from high-level programming languages like C, C++, or SystemC. This is particularly useful in complex designs, where creating an RTL description manually is time-consuming.

Detailed Explanation

High-Level Synthesis (HLS) simplifies the process of building hardware by allowing designers to write code in high-level programming languages, such as C or C++. Instead of manually creating detailed hardware descriptions (RTL), which can be very intricate and time-consuming, HLS automatically converts this high-level code into a lower-level representation that hardware can understand. This abstraction helps speed up the design process, especially for complicated systems where the details can become overwhelming.

Examples & Analogies

Think of HLS like cooking a complex dish. Instead of spending hours measuring and cutting ingredients individually (the RTL version), you follow a simple recipe (the high-level programming language) that tells you what to do step-by-step. The HLS takes care of all the detailed food prep for you, making the cooking experience faster and easier.

Scheduling in HLS

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Scheduling: HLS algorithms determine the order in which operations are performed, optimizing for both time and resource usage.

Detailed Explanation

Scheduling in the context of HLS refers to arranging the sequence of operations that need to be performed in the design. HLS algorithms analyze the operations to figure out the most efficient way to execute them, balancing how quickly tasks can be completed with how many resources (like memory or processing units) are available. Effective scheduling helps ensure that the design operates efficiently, reducing overall time delays and resource wastage.

Examples & Analogies

Consider scheduling tasks for a project. If you have several tasks to complete, scheduling them wisely means deciding which ones can be done simultaneously and which need to be done in a particular order. If you try to paint a wall while the paint is drying, you waste time. Similarly, HLS algorithms optimize the sequence of hardware operations to avoid delays and ensure efficient resource use.

Binding in HLS

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Binding: In HLS, binding is the process of assigning operations to hardware resources (such as functional units or memory). Efficient binding minimizes resource usage and optimizes power.

Detailed Explanation

Binding is a crucial step in HLS where the operations defined in the high-level code are mapped to actual hardware components. This involves deciding which functional units (like arithmetic logic units or memory storage) will carry out specific operations. The goal of efficient binding is to ensure that the hardware resources are used optimally, which ultimately saves power and reduces costs. By carefully assigning tasks to physical resources, designers can enhance system performance.

Examples & Analogies

Think of it like assigning roles in a theater play. Each actor (hardware resource) has a unique role (operation). If you assign multiple actors to the same role, you may waste talent and space, leading to inefficiency. Binding in HLS ensures that each operation has the best-suited actor performing it, optimizing the overall performance of the play (the hardware system).

Key Concepts

-

Scheduling: HLS algorithms define the sequence in which various operations take place within a design. Proper scheduling is crucial for optimizing both time and resource consumption, ensuring that the generated hardware operates efficiently.

-

Binding: This phase involves assigning specific hardware resources, such as functional units or memory elements, to the scheduled operations. Effective binding reduces resource utilization and enhances power efficiency, allowing the final hardware architecture to meet performance requirements.

-

HLS not only makes the design process more accessible but also enables rapid iterations and adjustments necessary for meeting performance metrics in modern VLSI systems. Overall, HLS generates efficient hardware implementations from complex high-level designs, decreasing the time-to-market for new technologies.

Examples & Applications

Using HLS, a designer could take a C++ algorithm for image processing and automatically generate an FPGA hardware configuration that implements the algorithm efficiently.

In embedded system designs, HLS can streamline the implementation of signal processing functions, enabling designers to focus on high-level functionality rather than low-level RTL details.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

HLS automates with great might, from high-level code to hardware in sight.

Stories

Imagine a builder (bind) who organizes workers (operations) in a way that every task happens at the right time (scheduling) to build a house efficiently (hardware design).

Memory Tools

The mnemonic ‘LEAP’ reminds us: Learn, Execute, Arrange, Performance for scheduling in HLS.

Acronyms

RAMP for Binding

Reduce

Assign

Minimize

Power.

Flash Cards

Glossary

- HighLevel Synthesis (HLS)

The process of converting high-level programming languages into hardware implementations.

- Scheduling

The task of determining the order of operations in HLS to optimize performance and resource usage.

- Binding

The assignment of scheduled operations to specific hardware resources in HLS.

Reference links

Supplementary resources to enhance your learning experience.