Logic Synthesis Algorithms

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome, everyone! Today we’ll explore the concept of logic synthesis in VLSI design, an essential process that transforms high-level design descriptions into gate-level representations. Can anyone tell me what you think a gate-level representation is?

I think it means the design is shown with specific logic gates, like AND or OR gates?

Exactly! Gate-level representations use actual logic gates to show how the circuit will function physically. Now, what do you think the primary goals of logic synthesis are?

Is one of the goals to optimize the design for area and power consumption?

Yes! Optimization is key. We typically want to minimize the number of gates while ensuring the performance remains satisfactory. Alright, remember the acronym A.P.P. for Area, Power, and Performance. Now, let’s discuss two critical tasks in logic synthesis.

Key Tasks in Logic Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

The main tasks involved in logic synthesis are optimization, technology mapping, Boolean minimization, and timing analysis. Let's break them down. Who can explain what technology mapping involves?

It’s like taking the logical design and finding real gates to use from a technology library, right?

Exactly! It ensures the logical functions are physically realizable. Now, can anyone tell me what Boolean minimization aims to achieve?

It tries to reduce the complexity of the logic expressions to make them easier to implement?

Right! By simplifying these expressions, we can make our circuits faster and cheaper. Let’s recall the two major categories of technology mapping: Cell-Based Mapping and Technology-independent Mapping. Can someone explain the difference?

Cell-based directly maps to specific gates while technology-independent first optimizes before mapping.

Great clarification! Remember, technology-independent mapping can often be more efficient. Let’s summarize these tasks briefly.

Boolean Minimization Algorithms

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's focus on Boolean minimization. Can anyone name a method or algorithm for this?

The Quine-McCluskey algorithm is one, right?

Yes! The Quine-McCluskey algorithm is exhaustive. It identifies and eliminates terms from a Boolean expression. Can anyone think of another method?

What about Karnaugh Maps? They’re useful for small functions!

Correct! K-Maps provide a visual way to simplify expressions and are much easier for functions with up to four variables. Lastly, who remembers a more heuristic approach?

The Espresso Algorithm is one, right?

Yes! The Espresso Algorithm is efficient for practical use. Remember this mnemonic: Q.K.E.B. for Quine-McCluskey, K-Maps, Espresso, and BDDs. Let’s have a quick recap of all these algorithms!

Timing and Power Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on to timing optimization, who can tell me about a technique related to this?

Static Timing Analysis, right? It ensures the circuit meets timing without simulation.

Exactly! And all timing paths must be checked for violations. How about power optimization techniques?

Clock gating is one; it turns off the clock to parts of the circuit to save power.

Correct! Reducing dynamic power is crucial, especially in larger designs. Can anyone list another optimization strategy?

We can also duplicate logic to speed up critical paths!

Great job! Now let’s summarize the importance of timing and power optimizations in modern designs.

High-Level Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, we encounter High-Level Synthesis or HLS. Can anyone explain what HLS does?

It automates generating hardware from high-level programming languages!

Correct! HLS can significantly reduce design time. What are two crucial parts of HLS?

Scheduling to determine the order of operations and Binding for resource assignments!

Perfect! Remember, efficient binding minimizes resource usage. As a quick recap, HLS streamlines complex designs — remember the acronym H.L.S. Finally, how do you think the discussion we had today will shape future designs?

It’ll likely lead to faster, more efficient tools in the industry!

Precisely! Let’s summarize today’s session and key concepts one last time.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Logic synthesis is a critical step in the VLSI design process, transforming high-level circuit descriptions into gate-level representations. This section explores key tasks associated with logic synthesis, including optimization, technology mapping, Boolean minimization, and techniques for sequential logic and power optimization.

Detailed

Logic Synthesis Algorithms

In modern VLSI design, logic synthesis serves as a vital transformation bridge, converting higher-level functional descriptions (written in HDL like VHDL or Verilog) into a gate-level circuit representation. The primary aim of this process is to optimize the resulting designs with respect to area, power, and performance efficiency.

Key Tasks in Logic Synthesis

Several principal tasks characterize the logic synthesis process:

1. Optimization of circuit size and components.

2. Technology Mapping, ensuring synthesized logic aligns with standard cell definitions from technology libraries.

3. Boolean Minimization to simplify logic functions.

4. Transforming designs from Register Transfer Level (RTL) to Gate-Level representation.

5. Timing Analysis to meet critical timing parameters.

Boolean Minimization Algorithms

Key algorithms that play a significant role include:

- Quine-McCluskey Algorithm: A comprehensive method for minimizing Boolean expressions.

- Karnaugh Maps (K-Maps): A visual simplification tool effective for small functions.

- Espresso Algorithm: A heuristic approach used in practical synthesis tools for efficient minimization.

- Binary Decision Diagrams (BDD): A representation method that facilitates manipulation and optimization of Boolean functions.

Technology Mapping

This involves mapping minimized Boolean functions to actual gates while meeting area and performance requirements.

- Cell-Based Mapping: Directly aligns Boolean functions to library cells.

- Technology-independent Mapping: Focuses on logic simplification before cell mapping, potentially offering greater efficiency but with computational costs.

Sequential Logic Synthesis

Sequential logic, characterized by memory components, involves designing systems like Finite State Machines (FSM) and implementing techniques like Pipelining to boost performance.

Power Optimization Techniques

Given the growing complexity of VLSI designs, implementing power reduction strategies is critical, including Clock Gating and Gate-Level Optimization strategies.

Timing Optimization**

Ensures circuits comply with timing constraints,

- Static Timing Analysis (STA) checks circuits without simulation.

- Retiming adjusts flip-flops for better timing performance.

- Logic Duplication enhances specific paths to balance circuit timing.

High-Level Synthesis (HLS)

HLS generates hardware from higher-level programming languages, facilitating efficient designs through Scheduling and Binding functions.

Through this chapter, it becomes clear that algorithms in logic synthesis are pivotal for transforming complex high-level designs into realizable circuits, ensuring that as designs evolve, synthesis approaches must advance equally to meet the demands of efficiency and performance.

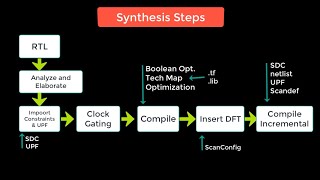

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Logic Synthesis in VLSI Design

Chapter 1 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Logic synthesis is a crucial step in the VLSI design process, where high-level functional descriptions (usually in hardware description languages like VHDL or Verilog) are transformed into a gate-level representation suitable for physical implementation. The main goal of logic synthesis is to optimize the design in terms of area, power, and performance. This process involves translating the behavioral or structural description of the circuit into a network of logic gates.

In this chapter, we will focus on the core algorithms used in logic synthesis, examining their approaches, advantages, and limitations.

Detailed Explanation

Logic synthesis is a fundamental stage in designing VLSI circuits, which are integrated circuits that combine thousands or millions of transistors. In this stage, designers take high-level descriptions, often written in specific programming languages like VHDL or Verilog, and convert them into a format usable by the manufacturing process, specifically as a network of logic gates. The main objectives here are to reduce the physical size of the circuit (area), use the least amount of power possible, and ensure that the performance is satisfactory, meaning that the circuit processes information quickly and reliably. It is critical to understand that this synthesis involves a detailed transformation, aiming to achieve efficiency while preparing the design for actual silicon implementation.

Examples & Analogies

Think of logic synthesis like translating a novel written in a complex language into a simple story for children. Just like the translator takes intricate ideas and distills them into a format that's easier to understand and appropriate for a different context (like children), logic synthesis takes high-level design languages, simplifies and restructures them into a format (logic gates) that can be physically built into a chip.

Key Concepts in Logic Synthesis

Chapter 2 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Logic synthesis involves several key tasks:

● Optimization: Minimizing the number of gates and the size of the circuit while meeting performance requirements.

● Technology Mapping: Mapping the synthesized logic to available standard cells (gates) from a given technology library.

● Boolean Minimization: Reducing the complexity of the Boolean functions that represent the logic design.

● Register Transfer Level (RTL) to Gate-Level: Converting RTL representations to gate-level representations.

● Timing Analysis: Ensuring that the design meets timing constraints, such as setup and hold times, propagation delays, and clock skew.

Detailed Explanation

In logic synthesis, several critical tasks are performed that ensure the final design is efficient and effective. Optimization involves trying to use the fewest number of gates possible, reducing the overall physical size of the circuit without sacrificing performance. Technology mapping takes the design and fits it to specific types of gates available in a technology library, which contains the different types of logic gates that can be used. Boolean minimization is about simplifying the Boolean functions that describe the logic, making them easier and more efficient to implement. The conversion from Register Transfer Level (RTL) to gate-level means changing the initial high-level design into detailed gate representations that can be constructed. Finally, timing analysis makes sure the design operates correctly within set temporal constraints, ensuring that signal timings are respected so that data flows correctly without errors.

Examples & Analogies

Imagine you are organizing a team to build a model of a skyscraper. Optimization is like deciding how to use the least amount of materials without compromising the skyscraper's integrity. Technology mapping would be identifying the different prefabricated parts you can use from a catalog and ensuring they fit your design. Boolean minimization is akin to simplifying complex architectural plans to avoid unnecessary lines and structures. RTL to gate-level conversion is like taking a detailed blueprint and breaking it down into individual components that can be constructed, while timing analysis would be similar to ensuring every part is built with enough time to set before the next part is added.

Boolean Minimization Algorithms

Chapter 3 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Boolean minimization plays a critical role in logic synthesis. It involves reducing the complexity of Boolean expressions, which can help reduce the area and delay of the resulting circuits. Several algorithms are used for Boolean minimization, with the most common being:

● Quine–McCluskey Algorithm: This is an exhaustive approach that systematically eliminates terms from a Boolean expression by combining pairs of terms that differ in only one variable. It’s widely used for minimization of small Boolean functions.

● Karnaugh Maps (K-Maps): K-Maps are used for simplifying Boolean expressions by visually grouping terms that can be combined. This is especially useful for simplifying expressions with up to four variables, where visual grouping is intuitive.

● Espresso Algorithm: This is a more efficient algorithm than the Quine–McCluskey approach, widely used in practical synthesis tools. It performs minimization through a series of heuristic steps to reduce Boolean expressions to their simplest form.

● Binary Decision Diagrams (BDD): BDDs represent Boolean functions as directed acyclic graphs, which make it easier to manipulate and optimize the Boolean functions. BDD-based algorithms are efficient and can be used for large-scale optimizations.

Detailed Explanation

Boolean minimization is a vital process in the logic synthesis phase, as the complexity of the Boolean expressions affects the efficiency of the circuits. By minimizing these expressions, you can lower the area needed for the circuit and reduce the delay in signal propagation within it. Different algorithms are deployed for this purpose: The Quine–McCluskey algorithm methodically combines pairs of terms that vary by one variable to minimize expressions, making it suitable for small functions. Karnaugh Maps simplify expressions through visual grouping, useful for functions up to four variables. The Espresso algorithm, more sophisticated and often more efficient, iteratively reduces Boolean expressions by applying heuristic methods. Binary Decision Diagrams offer a graphical representation that makes manipulation and optimization of Boolean functions more efficient, particularly for large sets of data.

Examples & Analogies

Consider you have a cluttered closet where you keep track of your clothes. Boolean minimization is like organizing that closet by getting rid of duplicate or unnecessary items, so you save space and make it easier to find what you need. The Quine–McCluskey method is like taking every item one by one and deciding which can be grouped together to save space, while Karnaugh Maps resemble visually arranging your clothes into categories so you can see what pairs with what. The Espresso algorithm is akin to regularly revisiting and refining your organization upgrades, and Binary Decision Diagrams act like a digital wardrobe management app that helps remind you of what you have and how to optimize your closet.

Technology Mapping

Chapter 4 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Once Boolean functions are minimized, the next step in logic synthesis is mapping these functions to actual gates from a given technology library. Technology mapping ensures that the logic is implemented using standard cells (e.g., AND gates, OR gates, multiplexers) in a way that meets both area and performance requirements.

The two main categories of technology mapping algorithms are:

● Cell-Based Mapping: This approach maps Boolean functions directly onto cells from the technology library. Algorithms like the A search algorithm are used to find the most efficient way to realize the Boolean function in terms of gates and connections.

● Technology-independent Mapping: This approach first optimizes the Boolean function without considering the actual gates available, and only later maps them to specific gates. This approach can be more efficient in terms of logic simplification but can be computationally expensive.

Detailed Explanation

After minimizing the Boolean functions, designers must map these simplified functions to physical gates in an actual technology library. This step is essential to ensure the resulting design is practical and can be manufactured. There are two primary methods of doing this: the first is cell-based mapping, which directly takes the minimized Boolean functions and matches them to available standard cells, choosing the best configurations to ensure efficiency. Algorithms like the A search algorithm help identify the optimal arrangements of gates and connections. The second method is technology-independent mapping, which focuses first on simplifying the Boolean function itself before considering which gates will implement it. This method could lead to better simplifications but might take longer to execute.

Examples & Analogies

Technology mapping is like a chef deciding on a recipe and the exact appliances to use. Cell-based mapping is like using a specific blender or knife directly from your kitchen tools that fit the recipe perfectly. In contrast, technology-independent mapping is akin to first deciding what you want to cook and what techniques will get the best results before selecting the specific kitchen tools. While you might save time by preparing an efficient recipe first, it may take longer to finalize what exactly you need later.

Sequential Logic Synthesis

Chapter 5 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

While much of logic synthesis focuses on combinational logic, sequential logic synthesis plays an equally important role in digital circuit design. Sequential circuits contain memory elements like flip-flops and latches, which are used to store information.

● Finite State Machines (FSMs): One of the key components of sequential logic design is the use of finite state machines (FSMs), which describe the behavior of circuits based on a finite number of states. Algorithms for synthesizing FSMs aim to optimize the number of states, state transitions, and the overall complexity of the FSM representation.

● Pipelining: This technique is used to improve performance by increasing the number of pipeline stages in sequential circuits. Logic synthesis algorithms often attempt to optimize the pipeline structure while minimizing the number of flip-flops used, to improve throughput and reduce latency.

Detailed Explanation

In addition to combinational logic, which doesn’t use memory and solely relies on current inputs to determine outputs, sequential logic incorporates memory elements that can store past inputs, crucial for many digital applications. The finite state machines (FSMs) are a fundamental part of this type of design, as they define how the system behaves based on its state at any given moment and how it transitions between states. The goal of designing FSMs is to minimize both the number of states needed and the transitions between them for streamlined performance. Pipelining is another key concept here, where the design is segmented into several stages, allowing multiple inputs to be processed at once. This boosts performance as it enhances throughput (the number of processes handled in a given time) and limits the delays caused by having too many sequential operations reliant on shared flip-flops.

Examples & Analogies

Think of sequential logic synthesis as organizing a relay race. Each runner represents a state in an FSM, with clear rules on when to pass the baton (the transitions). The design must optimize which runners (states) to use and how quickly they can pass the baton to maximize speed (performance). Pipelining is like having multiple races happening simultaneously on different tracks—each race with its own set of runners, allowing more athletes to complete laps faster, thereby improving overall race time.

Clock Gating and Power Optimization

Chapter 6 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As VLSI circuits become more complex, power optimization becomes a significant concern. Logic synthesis plays an essential role in reducing power consumption, with techniques such as:

● Clock Gating: This technique involves selectively turning off the clock to certain parts of the circuit when they are not in use. This can significantly reduce dynamic power consumption, especially in large designs.

● Gate-Level Power Optimization: Algorithms that reduce the switching activity of gates and optimize the logic design to minimize the number of switching events, thus reducing power consumption.

Detailed Explanation

Power optimization is an increasingly critical aspect of VLSI design due to the growing complexity of standardized circuits. As circuits become more intricate, ensuring they consume as little power as possible becomes essential. One effective method for doing this is clock gating—it allows the clock signal to be turned off for parts of the circuit that aren’t in use at any given time. This dramatically reduces the dynamic power consumption, as unused components are not energized. Another significant technique is gate-level power optimization, where algorithms analyze and modify the logic design to reduce the number of transitions that gates must undergo. Fewer transitions mean lower energy consumption, enhancing the overall efficiency and extending battery life in portable devices.

Examples & Analogies

Imagine you are managing energy use in a large house. Clock gating is akin to switching off the lights in rooms that aren’t in use, which saves energy. Just as you turn off lights to avoid wasting electricity, clock gating ensures that inactive circuit sections don't consume power. Gate-level optimization is like improving insulation and energy-efficient appliances in your home to minimize energy use, reducing how much power is needed while maintaining comfort.

Algorithms for Timing Optimization

Chapter 7 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing optimization ensures that the synthesized circuit operates within the required timing constraints. Several timing-related synthesis techniques are used to guarantee that the design meets the performance specifications:

● Static Timing Analysis (STA): STA is used to analyze the timing of a circuit without requiring simulation. It checks whether any paths in the design violate the timing constraints (e.g., setup and hold violations).

● Retiming: This technique involves shifting flip-flops in the circuit to optimize the timing of the design without changing its functionality. It can help reduce the critical path and improve clock frequency.

● Logic Duplication: Logic duplication involves duplicating certain logic elements to speed up critical paths. This helps to balance the circuit’s timing by reducing the delay of specific paths.

Detailed Explanation

Timing optimization is vital in ensuring that a circuit operates correctly at the desired speed. Timing constraints define the maximum allowable delays for signals to travel through the circuit. Techniques such as Static Timing Analysis (STA) check each potential signal path to ensure that it meets these constraints, identifying any issues without needing to run a full simulation of the circuit. Retiming works by adjusting the placement of flip-flops to better align with timing requirements, effectively moving them to achieve optimal operation without altering the circuit's intended function. Logic duplication helps by duplicating the circuits' logic elements strategically to help equalize timing across various paths, addressing any delays on critical pathways that could slow the circuit down.

Examples & Analogies

Imagine a busy highway where ensuring smooth traffic flow is essential—this is like timing optimization. Static Timing Analysis is similar to traffic engineers evaluating the road layout to find bottlenecks before they occur. Retiming is akin to adding and relocating traffic lights to maximize efficiency without changing the road's design. Logic duplication is like adding additional lanes to busy highways to ensure traffic can move more freely, thereby optimizing the time it takes for cars to travel the route.

High-Level Synthesis (HLS)

Chapter 8 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

High-Level Synthesis is an abstraction above traditional RTL synthesis. HLS algorithms automate the process of generating hardware from high-level programming languages like C, C++, or SystemC. This is particularly useful in complex designs, where creating an RTL description manually is time-consuming.

● Scheduling: HLS algorithms determine the order in which operations are performed, optimizing for both time and resource usage.

● Binding: In HLS, binding is the process of assigning operations to hardware resources (such as functional units or memory). Efficient binding minimizes resource usage and optimizes power.

Detailed Explanation

High-Level Synthesis (HLS) takes the design process a step further by allowing designs to be created at a higher level of abstraction, generally from programming languages like C or C++. Instead of manually detailing every low-level aspect of the design in RTL, HLS automates the conversion process, making it faster and often more efficient for complex designs. Within HLS, scheduling is crucial as it decides when each operation occurs, optimizing both the timing for execution and resource utilization. Binding refers to the assignment of specific hardware resources to the operations outlined in the high-level code, aimed at minimizing the amount of hardware used and conserving energy.

Examples & Analogies

Think of High-Level Synthesis like an automated kitchen where a chef simply provides a recipe in a general format (like a high-level programming language), and the kitchen automatically figures out which utensils and ingredients to use, and in what order. Scheduling is like organizing the cooking process to ensure each dish is prepared efficiently; you wouldn’t boil pasta while trying to bake a cake simultaneously if they require the same oven. Binding is akin to the kitchen assigning specific tools (like pots and pans) to each step of the recipe, ensuring smooth cooking while minimizing the number of tools spread across the counter.

Conclusion

Chapter 9 of 9

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this chapter, we have delved into the essential logic synthesis algorithms that form the backbone of modern VLSI design. From Boolean minimization techniques like Espresso to technology mapping, timing optimization, and sequential synthesis, each algorithm plays a vital role in transforming high-level designs into efficient, manufacturable circuits. As the scale and complexity of VLSI designs continue to increase, the importance of efficient synthesis algorithms becomes even more critical. In the following chapters, we will explore these algorithms further and see their application in industry-standard VLSI design tools.

Detailed Explanation

This chapter has covered the fundamental algorithms underlying logic synthesis, highlighting their significance in modern VLSI design. We learned about Boolean minimization techniques, which reduce circuit complexity, to improve efficiency; technology mapping methods that ensure designs are implemented with actual hardware; and timing optimization strategies that guarantee circuits operate within specified constraints. Each method contributes uniquely to the process of transforming abstract, high-level design into concrete, manufacturable products. Understanding and refining these algorithms is increasingly important as semiconductor technologies evolve and designs grow more complex, impacting how circuits are made in the future.

Examples & Analogies

Think of the logic synthesis process like preparing for a large concert. Each algorithm is a step in the planning, from ensuring all musical pieces are arranged (Boolean minimization), to organizing the band members (technology mapping), ensuring everything is on time (timing optimization), and finally coordinating the entire event to flow smoothly (high-level synthesis). The concert wouldn’t succeed without careful planning, just as VLSI designs require rigorous logic synthesis to function optimally.

Key Concepts

-

Optimization: The goal is to reduce the number of gate elements while maintaining circuit performance.

-

Technology Mapping: Matching synthesized logic to actual gates found in technology libraries.

-

Boolean Minimization: Simplifying Boolean functions to reduce complexity.

-

Timing Analysis: Confirming there are no timing violations in the circuit design.

-

High-Level Synthesis: Generating hardware design from high-level programming languages.

Examples & Applications

Using the Quine-McCluskey algorithm to minimize the Boolean function F(A,B,C) = A'B + AB' + AC can lead to a simpler function.

Karnaugh Maps (K-Maps) can simplify a function like F(X,Y,Z) = Σ(0, 1, 3) to a simpler form with fewer terms.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In synthesis, circuits must glisten; optimize well to meet the plan, or for performance, power will be a sham.

Stories

Once there was a circuit designer named Sam who wanted to make the quickest circuit. He learned about timing analysis, clock gating, and Boolean minimization to make his design efficient and quiet, much like how a careful chef whips up a perfect meal by balancing flavors and time.

Memory Tools

Remember A.P.P for logic synthesis: Area, Power, and Performance.

Acronyms

Use Q.K.E.B. to remember key Boolean minimization algorithms

Quine-McCluskey

K-Maps

Espresso

and BDDs.

Flash Cards

Glossary

- Logic Synthesis

The process of converting high-level functional descriptions of a circuit into a gate-level implementation.

- Boolean Minimization

Techniques to simplify Boolean functions, reducing circuit complexity.

- Technology Mapping

Mapping a synthesized logic representation onto specific gates from a technology library.

- Static Timing Analysis (STA)

A method to analyze circuit timing without simulation to check for timing violations.

- HighLevel Synthesis (HLS)

Automating the generation of hardware from high-level programming languages.

Reference links

Supplementary resources to enhance your learning experience.