Clock Gating and Power Optimization

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Clock Gating

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll be discussing clock gating. Does anyone know what clock gating is?

Isn't it about controlling the clock signal to reduce power?

Exactly! Clock gating allows us to selectively disable the clock signal to parts of a circuit that aren't in use, significantly reducing dynamic power consumption. Remember, less active time means less power!

So it's like turning off the lights in a room that's not being used?

That's a perfect analogy! Just as you turn off lights to save electricity, we can turn off the clock in certain circuit sections. This concept is crucial in large designs.

How does this significantly affect power savings?

Great question! Since dynamic power consumption is proportional to the switching activity, by gating the clock, we can dramatically decrease unnecessary transitions, which saves energy. Remember the acronym 'CCP' - Clock Control Power - to help you recall this principle.

Can clock gating be applied to all circuits?

It can be applied broadly but with some considerations for circuit design and operational limits. Always think about where it can be best implemented for maximum efficiency.

To summarize, clock gating is a technique to reduce power consumption by selectively disabling parts of the circuit. It's essential to smart power management in circuit designs.

Gate-Level Power Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s shift our focus to gate-level power optimization. Who can tell me why it's essential?

Is it to minimize how often the gates switch?

Exactly! By reducing the number of switching events, we can decrease power consumption significantly. Gates consume power during the transitions – the more transitions, the higher the power use!

Are there specific techniques we can use in gate-level optimization?

Yes, common approaches include simplifying logic expressions, minimizing gate counts, and design adjustments to reduce toggle rates. Keep in mind the term 'LOW POWER,' which can help remind you of the goal here.

Could you explain what you mean by simplifying logic expressions?

Certainly! Simplifying logic expressions means reducing the complexity of the Boolean equations used in circuits. By simplifying, we reduce the number of gates required, leading to fewer transitions and lower power use.

How do we measure if our power optimization techniques are effective?

Good point! Power analysis tools can simulate and measure your circuit's power consumption under various conditions. Monitoring these metrics can help us gauge the effectiveness of our strategies.

In summary, gate-level optimization plays a vital role in reducing the switching activity of gates to lower power consumption, emphasizing the importance of smart design choices.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

As VLSI circuits evolve in complexity, power consumption becomes a major concern. This section emphasizes clock gating as a means to selectively turn off power to unused circuit parts and discusses gate-level optimization to minimize switching activity and power usage, essential for efficient logic synthesis.

Detailed

Clock Gating and Power Optimization

As technology advances, the complexity of Very Large Scale Integration (VLSI) circuits increases, leading to significant power consumption challenges. Power optimization is a critical phase in the logic synthesis process, primarily focused on reducing energy usage in designs.

Clock Gating

Clock gating is a prominent technique employed to reduce dynamic power consumption. By selectively turning off the clock signals to certain parts of the circuit when they are not actively processing data, overall power usage can decrease greatly. The ability to 'gate' the clock is particularly important in larger designs where different components may remain inactive at various times during operation.

Gate-Level Power Optimization

In addition to clock gating, another major strategy involves gate-level power optimization. This process focuses on reducing the switching activity of logic gates within the design. By optimizing the logic configuration, the number of switching events - where gates change states from high to low or vice versa - can be minimized. This reduction has a direct impact on lowering power consumption, making it a vital consideration during the synthesis process.

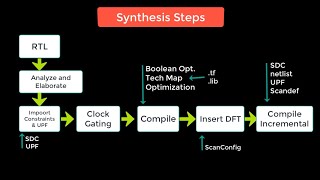

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Power Optimization

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As VLSI circuits become more complex, power optimization becomes a significant concern. Logic synthesis plays an essential role in reducing power consumption, with techniques such as:

Detailed Explanation

This chunk introduces the concept of power optimization in Very Large Scale Integration (VLSI) circuits, emphasizing its importance due to the increasing complexity of circuits. Power optimization is crucial because excess power consumption can lead to higher heat generation, reduced battery life in portable devices, and increased operating costs in large systems.

Examples & Analogies

Think of power optimization in VLSI circuits like managing electricity use in a smart home. Just as a smart home system can turn off lights or lower the thermostat when rooms aren’t in use to save energy, VLSI circuits must find ways to limit power consumption when certain parts aren’t actively needed.

Clock Gating Technique

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Clock Gating: This technique involves selectively turning off the clock to certain parts of the circuit when they are not in use. This can significantly reduce dynamic power consumption, especially in large designs.

Detailed Explanation

Clock gating is a method used in circuit design to conserve power. The idea is that many parts of a circuit do not need to be active all the time. By turning off the clock signal (which drives the operation of the circuit) to sections that are not in use, designers can reduce dynamic power consumption. This is particularly beneficial in large designs where many components could otherwise unnecessarily consume power.

Examples & Analogies

Imagine having a refrigerator that works all the time, even when it's empty. If the fridge could sense when it's empty and turn itself off, it would save a significant amount of energy. Similarly, clock gating helps circuits save energy by preventing unnecessary operations.

Gate-Level Power Optimization

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Gate-Level Power Optimization: Algorithms that reduce the switching activity of gates and optimize the logic design to minimize the number of switching events, thus reducing power consumption.

Detailed Explanation

Gate-Level Power Optimization focuses on minimizing the power consumed by the logic gates in a circuit. This is achieved by reducing the switching activity, which refers to how often the gates change from one state to another (like turning on and off). Each time a gate switches, it consumes dynamic power. By optimizing the logic design to decrease the number of switching events, overall power consumption can be minimized.

Examples & Analogies

Consider a traffic light system. If the lights switch too often or are programmed inefficiently, a lot of energy is wasted. By optimizing which lights change and when, we can keep the energy use down while maintaining smooth traffic flow, similar to how gate-level optimization reduces unnecessary power use in circuits.

Key Concepts

-

Clock Gating: A method to reduce power by turning off the clock signal in non-active circuit areas.

-

Power Optimization: Techniques applied to reduce the power consumption of VLSI circuits.

-

Switching Activity: The rate of toggling of logic gates, directly affecting power usage.

Examples & Applications

Example of clock gating includes disabling clock signals to sections of a microprocessor that aren't currently processing tasks.

Gate-level power optimization could involve redesigning a circuit to minimize unused gate states during operation.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Turn off the clock when circuits are slack, save some power, keep the output intact.

Stories

Imagine a busy restaurant where only certain tables are served at any given time. By locking the doors to the unoccupied areas, the restaurant saves energy, just like clock gating saves power.

Memory Tools

C for Clock, G for Gating - together they help reduce our rate of power waiting.

Acronyms

GPO

Gate Power Optimization - a reminder of the strategy focus for circuit efficiency.

Flash Cards

Glossary

- Clock Gating

A power optimization technique that selectively turns off the clock signal to parts of a circuit that are not in use.

- Dynamic Power

The power consumed by a circuit due to transitions between logical states.

- Switching Activity

The frequency or rate at which a logic gate transitions between its on and off states.

Reference links

Supplementary resources to enhance your learning experience.