Advanced Components and Techniques for Enhancing Testability

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Advanced Fault Modeling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will begin with advanced fault modeling. Why do you think traditional fault models might fail in complex designs?

Maybe because they don't cover all types of faults?

Exactly! Traditional models often overlook timing-related faults. One essential type to consider is delay faults, which occur when signals don't propagate on time.

What are transition and path delay faults?

Great question! Transition faults focus on ensuring the timing of signal changes is correct, while path delay faults check the timing across multi-clock systems. Remember the acronym 'DPT' for Delay, Path, Transition faults?

Got it! What do we do when we identify these faults?

We use advanced models to detect and correct any timing violations, which is crucial for high-speed circuits.

So, can we trust these models to improve efficiency?

Absolutely! They help ensure our designs are reliable and effective. Let's summarize: advanced fault models detect complex failures, focusing on delaying and path-related issues.

Test Access Mechanisms

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's delve into test access mechanisms, or TAMs. Why do you think accessibility is essential in testing?

To simplify how we check internal components?

Exactly! TAMs allow better communication between test equipment and system components. Can someone explain a critical component of TAMs?

Is JTAG part of it?

Yes! The JTAG interface facilitates accessing internal signals. With advancements, we can handle complex systems effectively. Remember ‘TAP’ for Test Access Ports?

And what about the hierarchical aspect?

Good catch! Hierarchical TAM applies testability across component and subsystem levels, ensuring efficient testing in complex setups.

So better TAM means better reliability?

That's right! Efficient TAM significantly enhances overall testability. In summary, TAMs improve internal communication, especially with JTAG and hierarchical approaches.

Power-Aware Testing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's talk about power-aware testing. Why is this approach gaining relevance today?

Because energy consumption is a major concern now?

Exactly! Power-aware testing focuses on minimizing energy use during testing. Could anyone share a method to achieve this?

Low-power test patterns?

Correct! By optimizing low-power patterns, we can reduce dynamic power consumption. What about power gating?

Isn't that when we shut off power to unnecessary parts during testing?

Exactly right! Power gating helps extend battery life, especially for embedded devices. Let's recap: power-aware testing reduces energy consumption and promotes system efficiency.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore advanced fault modeling methods, effective test access mechanisms, and power-aware testing techniques that address the complexities of contemporary electronic circuits. Key insights include the identification of timing-related faults, the role of test access ports, and strategies for minimizing power consumption during testing.

Detailed

Advanced Components and Techniques for Enhancing Testability

This section examines emerging components and techniques that are elevating testability in complex electronic systems. As circuits become more sophisticated, traditional methods of handling faults and efficiencies require adaptation and enhancement.

10.3.1 Advanced Fault Modeling

Advanced fault models are critical as they address complex failures in modern designs, focusing on:

- Delay Faults: Issues arising when signal propagation doesn't meet timing constraints, which could lead to system malfunction. Enhanced fault models for these situations aid in detecting and correcting timing violations in high-speed circuits.

- Transition and Path Delay Faults: Emphasizing the need for precise timing of signal transitions across multi-clock systems to ensure proper functioning.

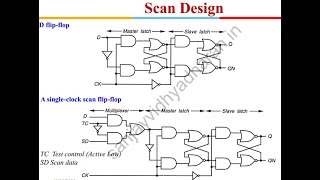

10.3.2 Test Access Mechanisms

Efficient Test Access Mechanisms (TAM) are vital for improving testability, particularly in System-on-Chip (SoC) architectures. Key aspects include:

- Test Access Ports (TAP): JTAG interfaces remain essential for internal signal access and control during testing. Evolving TAP designs are tasked with managing the demands of high-speed, multifunctional systems.

- Hierarchical TAM: This approach enables testability implementation at various system levels, from single components to entire subsystems, promoting effective testing practices in complex multi-core designs.

10.3.3 Power-Aware Testing

Power-aware testing becomes critical due to increasing energy consumption concerns. This technique focuses on:

- Low-Power Test Patterns: Patterns that are optimized to reduce power usage during testing phases.

- Power Gating: Implementing power gating in non-essential system areas during test phases to preserve battery life in embedded systems.

The integration of these advanced techniques highlights the evolving landscape of design for testability, ensuring that electronic systems remain efficient, reliable, and adaptable to an ever-growing complexity.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Advanced Fault Modeling

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As circuits become more intricate, traditional fault models need to evolve to handle new types of faults. Advanced fault models are being developed to address more complex failure mechanisms that arise in modern designs, such as timing-related faults and non-ideal behaviors in mixed-signal circuits.

- Delay Faults: These faults occur when signals do not propagate through the circuit within the required timing parameters, which can lead to malfunctioning systems. Advanced fault models for delay faults help in detecting and correcting timing violations in high-speed circuits.

- Transition and Path Delay Faults: These models focus on ensuring that the timing of signal transitions is correct across all paths, particularly in multi-clock or high-speed systems.

Detailed Explanation

Advanced Fault Modeling refers to the need for updated fault models as circuit designs grow more complex. Traditional models may not effectively capture new types of faults such as timing issues that occur when signals take too long to travel through the circuit. Two key types of advanced fault models focus on these issues: Delay Faults, which look at timing violations, and Transition and Path Delay Faults, which ensure signals change states at the right times across different paths. These fault models are critical in ensuring the reliable operation of high-speed and intricate circuits.

Examples & Analogies

Think of a busy intersection where cars need to reach their destination within a specific time. If some cars are delayed in reaching the intersection (similar to Delay Faults), it may cause congestion and accidents (malfunctions). Advanced systems would monitor traffic signals to ensure all cars transition correctly through the intersection without delays (similar to Transition and Path Delay Faults).

Test Access Mechanisms

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Effective test access mechanisms (TAM) are essential for improving testability, especially in complex SoC designs. TAMs enable efficient communication between the test equipment and the components inside the system.

- Test Access Ports (TAP): The JTAG interface remains a critical tool for accessing internal signals and controlling test execution. Advanced TAP interfaces are being developed to handle high-speed, multi-functional systems with large-scale integration.

- Hierarchical TAM: Hierarchical test access mechanisms allow testability features to be applied at different levels of the system, from individual components to entire subsystems. This hierarchical approach enables efficient testing of multi-core and multi-functional designs.

Detailed Explanation

Test Access Mechanisms (TAM) are vital tools in ensuring that testing equipment can effectively communicate with various components within sophisticated circuit designs. One example includes Test Access Ports (TAP), which allow engineers to access internal data for testing purposes. The JTAG interface is a common type of TAP that has evolved to meet the demands of fast, complex systems. Hierarchical TAM expands this concept by allowing testing capabilities to be organized at different levels, enabling thorough testing of intricate systems by targeting individual components and subsystems.

Examples & Analogies

Imagine you are trying to repair a complex machine with many interconnected parts, like an engine. If you only have access to the outer shell, it may be difficult to troubleshoot issues. A Test Access Mechanism is like having strategically placed access panels in the machine that let you reach the internal components easily. Hierarchical access is like having several tiers of panels; opening one gives you access to a group of parts, while diving deeper allows you to focus on individual components.

Power-Aware Testing

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As energy consumption becomes a key concern in modern electronics, power-aware testing is emerging as an essential technique. This approach involves designing test patterns that minimize power consumption during the testing phase.

- Low-Power Test Patterns: By optimizing the switching activity of test patterns, power-aware testing reduces the dynamic power consumption of the system during test.

- Power Gating During Testing: Power gating can be applied to parts of the system that are not needed for testing, reducing unnecessary power consumption and extending battery life in mobile and embedded devices.

Detailed Explanation

Power-Aware Testing is an approach tailored to meet the challenges of energy efficiency in electronic devices. It encompasses two main strategies: designing test patterns to minimize the amount of energy used when the device is being tested (Low-Power Test Patterns) and powering down parts of the system that are not needed during testing (Power Gating). By focusing on these aspects, engineers can carry out tests without significantly draining the battery or consuming a lot of power.

Examples & Analogies

Imagine planning for a road trip with a hybrid car. You would want to choose routes that save fuel while still allowing you to reach your destination efficiently. Similarly, Power-Aware Testing optimizes patterns to use less power, just like tracking routes to ensure the car uses the least fuel possible during travel. Power Gating is like only using the engine when needed and turning it off when cruising downhill.

Key Concepts

-

Advanced Fault Modeling: Enhanced methods to detect and address timing-related faults in circuits.

-

Test Access Mechanisms (TAM): Strategies for improving communication between test equipment and components.

-

Power-Aware Testing: Techniques that reduce energy consumption during testing phases.

Examples & Applications

Using JTAG as a Test Access Mechanism to gain access to signal behaviors in a circuit.

Implementing low-power test patterns to minimize power usage in portable devices during testing.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When timing's not right, circuits take flight; fix the delay to keep systems bright.

Stories

Imagine a racer who can't keep the pace because the signals in the circuit are too late. Advanced fault models help this racer stay on track and ensure they finish the race without falls.

Memory Tools

Remember 'DPT' for Delay, Path, Transition to keep track of key fault types!

Acronyms

TAP

Test Access Port for easy insight into circuit tests!

Flash Cards

Glossary

- Fault Model

A framework used to represent and analyze faults within electronic circuitry.

- Delay Fault

A fault occurring when a signal does not propagate through a circuit within designated timing parameters.

- Transition Fault

A fault concerning incorrect timing of signal transitions in circuits.

- Test Access Mechanism (TAM)

Tools and protocols that facilitate the connection between test equipment and internal circuit components for testing purposes.

- PowerAware Testing

Testing methods designed to minimize power consumption during the testing phase of electronic components.

Reference links

Supplementary resources to enhance your learning experience.