Test Pattern Compression

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Test Pattern Compression Overview

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss test pattern compression, a critical technique in the field of Design for Testability. With increasingly complex circuit designs, why do you think it's important to compress test patterns?

So we can reduce the amount of data that needs to be managed during testing?

Exactly! Compression helps us use fewer resources while maintaining the quality of our tests. Let's talk about some specific compression techniques, like dictionary-based compression. Can anyone guess how it might work?

Maybe it uses a reference table for common patterns?

Correct! It uses a dictionary to replace lengthy repeating sequences with shorter identifiers. This makes the test data more manageable. Remember the acronym 'D-C-R' for Dictionary-based Compression and Reduction.

Got it! D-C-R for easy recall.

Well done! In summary, test pattern compression is crucial for efficient testing of complex systems, utilizing methods like dictionary-based compression.

Test Minimization Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we've covered compression, let's move to test minimization. Who can tell me what we mean by test minimization?

It's about reducing the number of test patterns while ensuring we still find all the faults?

Exactly! By minimizing test patterns, we can achieve efficient testing. Techniques like greedy and genetic algorithms help identify and eliminate redundant patterns. Can anyone think of a scenario where this might be helpful?

Maybe in large-scale testing with limited time and resources?

Perfect! Less redundancy means more efficiency in constraints like time. Remember the mnemonic 'G-G-E' for Greedy, Genetic, Efficiency to recall the importance of these strategies.

I see how important this is for large systems!

Good observations! So, to recap, minimizing test vectors increases testing efficiency without compromising fault detection.

Partial Scan Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's move on to partial scan optimization—any initial thoughts on this approach?

Is it about testing only part of a system to save time?

That's right! By enabling scan mode for just part of the system, we can reduce testing time and required flip-flops. How do you think this impacts fault coverage?

As long as we cover critical areas, it should maintain coverage, right?

Exactly! Focusing testing on important regions can help achieve high fault coverage. Remember the acronym 'P-C-O' for Partial Chain Optimization to recall this concept.

P-C-O is an easy way to remember!

Great! In summary, partial scan optimization maintains high coverage while improving efficiency.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Test pattern compression is crucial for handling the complexity of modern electronic systems. The section outlines methods like dictionary-based compression and run-length encoding to minimize test vector size, alongside test minimization strategies that focus on eliminating redundancy to enhance fault coverage without compromising testing thoroughness.

Detailed

Test Pattern Compression

As electronic circuit designs grow increasingly complex, the volume of test data required to ensure thorough testing also rises significantly. This section explores test pattern compression techniques which aim to diminish the size of test vectors, thereby speeding up the testing process and reducing memory requirements without sacrificing fault coverage.

Key Techniques:

-

Test Pattern Compression:

- Methods like dictionary-based compression and run-length encoding effectively decrease the size of test patterns. These techniques yield more compact and efficient representations of test data, which facilitate the testing of larger systems, ultimately leading to shorter testing times and reduced costs.

-

Test Minimization:

- Focuses on identifying and removing redundant test patterns while ensuring high fault coverage. Techniques such as greedy algorithms and genetic algorithms are utilized for this purpose. By minimizing the number of necessary test vectors, these approaches enhance testing efficiency without compromising fault detection capabilities.

-

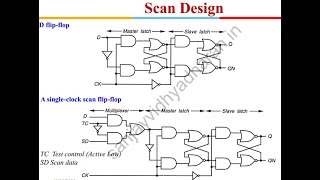

Partial Scan Optimization:

- In some circuit designs, utilizing partial scan chains can result in significant benefits. By enabling scan mode for only selected portions of the system, this approach conserves area and testing time while still achieving high fault coverage.

Through these innovations in test pattern compression, engineers can maintain a balance between comprehensive testing and practical resource utilization, adapting to the demands of modern electronic systems.

Youtube Videos

Key Concepts

-

Test Pattern Compression: A technique aimed at reducing the size of test vectors.

-

Dictionary-Based Compression: An approach that uses a reference dictionary to identify and store repetitive sequences.

-

Test Minimization: The process of identifying and eliminating redundant test vectors while maintaining high fault coverage.

-

Partial Scan Optimization: A testing approach that enables testing only parts of a system, improving efficiency.

Examples & Applications

An example of dictionary-based compression could involve a set of test vectors like {AAAA, BBBB, AAAA, CCCC}. Using compression, this set may be represented as {A(2), B(1), C(1)}.

For test minimization, imagine a scenario where a set of test vectors initially contains 100 patterns, but after applying an algorithm, we discover that only 60 patterns remain essential for fault detection.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To save time and not make a mess, compress those patterns - it's the best!

Stories

Imagine a massive library filled with books on similar subjects. If it only keeps the essential volumes, it can be accessed faster. Similarly, by compressing test patterns, a circuit's testing demands become manageable and swift.

Memory Tools

Use 'CC-GP' for 'Compression, Compression; Greedy, Patterns' to remember key concepts of the section.

Acronyms

D-C-R for Dictionary-Based Compression and Reduction.

Flash Cards

Glossary

- Test Pattern Compression

A method of reducing the size of test patterns to create more compact test data for efficient circuit testing.

- DictionaryBased Compression

A technique that replaces long repeating sequences in test patterns with shorter references stored in a dictionary, thus compressing the total size.

- Test Minimization

The process of reducing the number of test vectors required to achieve high fault coverage, often involving algorithms to identify and eliminate redundancy.

- Partial Scan Optimization

A method that places only part of a system in scan mode during testing to save time and resources while still ensuring adequate fault coverage.

Reference links

Supplementary resources to enhance your learning experience.