Introduction to Advanced Topics in Design for Testability

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Overview of DFT Evolution

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome class! Today we are diving into the evolution of Design for Testability, or DFT. Why do you think traditional DFT methods may be insufficient for modern circuits?

Because electronic systems are becoming more complex, especially with SoCs and multicore designs.

Exactly! As systems evolve, we must adapt our testing techniques to improve fault coverage and efficiency. Can anyone name one of the advanced techniques we will explore?

Automated test generation!

Great point! Automated test generation using AI enhances our testing capabilities significantly. If we think of DFT, remember the acronym � 'FATE' - Fault coverage, Automation, Test efficiency, and Effectiveness. This can help us remember the main goals of modern DFT.

AI-Driven Approaches

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's talk about AI-driven test generation. How does AI help in producing test patterns?

AI can analyze the circuit design and automatically create test vectors, which saves time.

Correct! Additionally, AI can learn from data to improve fault detection. This means more accurate identification of subtle faults. Can anyone explain how this might impact the design process?

It allows engineers to predict weaknesses early and address them, improving test coverage.

Exactly! Remember, the quicker we can catch design flaws, the less rework is needed later. Let's summarize: AI enhances test generation and fault detection, streamlining the overall testing process!

Test Compression Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we will cover test compression. Why is it essential for modern electronic systems?

Because the amount of test data increases with circuit complexity, and we need smaller test patterns.

Exactly right! By using techniques like dictionary-based compression, can anyone tell me how this affects testing time and cost?

It should reduce both since smaller data means it takes less time to test and less memory.

Well said! Always consider efficiency in design—using the acronym 'COMPRESS' can help: Compressing Operating Memory to Reduce Expenses in Testing Systems.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

As electronic systems evolve, traditional DFT techniques must adapt to the growing complexity of circuits. This section discusses emerging trends in DFT that aim to improve testing efficiency, fault coverage, and cost-effectiveness in advanced systems like SoCs and multicore processors.

Detailed

Detailed Summary

In the section Introduction to Advanced Topics in Design for Testability, we explore the critical evolution of Design for Testability (DFT) as electronic systems, particularly System-on-Chip (SoC) designs, continue to advance. The increasing complexity of these designs necessitates a shift from traditional DFT methodologies to innovative approaches that enhance testing capabilities.

Among the primary emerging trends in DFT, the following are highlighted:

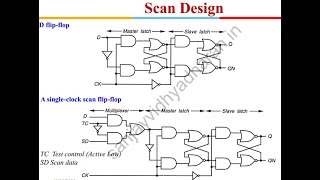

- Scan-Based Testing: Improved techniques in scan testing are vital to manage the complexity of circuits effectively.

- Automated Test Generation: Utilizing artificial intelligence (AI) to automate the generation of test vectors can significantly enhance fault coverage and decrease human effort involved in test development.

- Test Compression: To cope with larger test data sizes, advanced compression techniques are implemented, leading to more efficient testing processes.

- Self-Test Systems: These systems integrate testing capabilities and fault recovery mechanisms to maintain functionality without human intervention.

- AI-Assisted Testing: Leveraging AI can help optimize the overall testing efficiency and predict potential faults in designs.

The significance of these advancements lies in their potential to facilitate more efficient, cost-effective testing, ultimately addressing the needs of modern electronic devices.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Evolving Electronic Systems

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As electronic systems continue to evolve, traditional Design for Testability (DFT) techniques must adapt to meet the increasing complexity of circuits, particularly in system-on-chip (SoC) designs, multicore processors, and advanced memory systems.

Detailed Explanation

Electronic systems are becoming more advanced with time. This means the techniques we use to design them for testing (called Design for Testability or DFT) also need to change and improve. As we see more complex designs like system-on-chip (SoC), multicore processors, and advanced memory systems, traditional methods of DFT may not be enough. Therefore, updates and advancements in testing strategies are critical to ensure these systems can be effectively tested.

Examples & Analogies

Think of DFT techniques like a car's maintenance schedule. As cars evolve with new technologies like electric engines and self-driving capabilities, some of the old maintenance practices may not apply. Just as mechanics need to adapt their skills and tools to service these newer models, engineers must refine their DFT methods to keep pace with the evolution of electronic systems.

Emerging Trends in DFT

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Emerging trends in DFT aim to address the challenges of scaling testability for these advanced systems while also improving testing efficiency, fault coverage, and cost-effectiveness.

Detailed Explanation

As electronic systems grow more complex, new trends in DFT are emerging to solve the challenges associated with testing these designs. These trends focus on making testing more efficient, improving how well we can detect faults (fault coverage), and doing all this without significantly raising costs. It's important to balance these factors so that testing remains effective and does not break the budget.

Examples & Analogies

Imagine you're a chef in a restaurant that has recently introduced a new, complex dish. You need to ensure that each ingredient is just right and that the dish is presented beautifully. To succeed, you might adopt new kitchen tools or techniques to streamline your cooking process, improve presentation, and keep costs manageable while adapting to this new demand.

Focus of the Chapter

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This chapter delves into the advanced components and techniques that are enhancing testability, focusing on the latest advancements in scan-based testing, automated test generation, test compression, self-test systems, and AI-assisted testing.

Detailed Explanation

This chapter will explore various advanced elements and methods that are contributing to improved testability in electronic systems. It will look into cutting-edge advancements such as scan-based testing (a method of testing digital circuits), automated test generation (which uses algorithms to create testing procedures), test compression (which reduces the amount of test data needed), self-test systems (that can perform tests on themselves), and AI-assisted testing (where artificial intelligence aids in the testing process). Each of these advancements plays a critical role in making testing more efficient and effective.

Examples & Analogies

Consider a gym instructor who constantly updates their training methods and equipment based on the latest fitness trends. Just like the instructor uses the newest workout routines and tools to improve clients' fitness levels, engineers utilize the latest techniques in DFT to enhance their testing abilities, ensuring that electronic systems function well and meet modern demands.

Significance of Advanced DFT Techniques

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

These trends are shaping the future of DFT, enabling the design of testable systems that can handle the growing demands of modern electronic devices.

Detailed Explanation

The advancements in DFT techniques discussed in this chapter are crucial for the future of electronic design. They ensure that as we continue to create increasingly sophisticated devices, we also have effective ways to test them. This helps in detecting flaws that could impact performance, reliability, and safety, ultimately resulting in the development of robust products that meet modern user expectations.

Examples & Analogies

Think of it like the evolution of smartphones. As technology advances, phones become more feature-rich and complex. However, manufacturers also invest in rigorous testing processes to ensure that every feature works flawlessly before the device reaches consumers. Just like smartphone manufacturers must keep up with advancements in technology while ensuring quality, engineers in DFT must develop advanced testing methods to maintain the reliability of modern electronic devices.

Key Concepts

-

Emerging DFT Techniques: The need for advanced techniques like AI and automated generation in today's electronic designs.

-

Testing Efficiency: Importance of efficient testing methods to reduce time and cost in complex designs.

-

Complex Systems: Understanding that modern electronic systems require innovative testing strategies.

Examples & Applications

An AI algorithm generating test vectors for a complex SoC to maximize fault coverage while minimizing the time spent on testing.

Using dictionary-based compression to reduce test patterns size in a multicore processor design, leading to lower memory usage and quicker assessments.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In testing, we compress to impress, fewer patterns, less stress!

Stories

Imagine an engineer who designed a complex chip. By using AI for test generation, they cut their testing time in half! A little robot named Testa helped find the sneaky faults—now every design passed with flying colors!

Memory Tools

RAPID - Relevant Automated Patterns In DFT helps to recall key advantages of automated testing.

Acronyms

FATE - Fault coverage, Automation, Test efficiency, Effectiveness.

Flash Cards

Glossary

- Design for Testability (DFT)

A methodology that improves the ease of testing a design to ensure it operates correctly.

- SystemonChip (SoC)

An integrated circuit that incorporates all components of a computer or other electronic system into a single chip.

- Automated Test Generation

The use of software tools and AI to automatically create test patterns.

- Test Compression

Techniques that reduce the size of test patterns to enhance efficiency.

- SelfTest Systems

Systems that embed testing capabilities allowing them to detect and mitigate faults autonomously.

- Fault Coverage

The measure of the proportion of faults detectable by the test set used in testing.

Reference links

Supplementary resources to enhance your learning experience.