Test Access Mechanisms

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Test Access Mechanisms

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss test access mechanisms, or TAM. Can anyone tell me why these might be important in electronic systems?

Isn't it about making it easier to test components within complex systems?

Exactly, Student_1! TAMs enhance the testability of complex designs like System-on-Chips or SoCs. Can anyone think of specific components of a TAM?

What about the Test Access Port, like the JTAG interface?

Correct! The JTAG interface is vital for accessing internal signals. Great job, let's move to how TAMs are structured.

Test Access Ports (TAP)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s dive deeper into Test Access Ports, or TAP. Who can explain how TAP is used in testing?

It connects the testing equipment to the internal parts of the chip, right?

Exactly, Student_2! And what are some advancements being made in TAPs for modern systems?

They are being developed to support high-speed and multifunctional systems.

Well done! This is vital as the complexity of chips increases.

Hierarchical TAM

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s discuss hierarchical test access mechanisms. Why do we use a hierarchical setup?

It helps to efficiently apply testability features at different levels, like parts of a system.

Exactly, Student_3! How does this affect testing multi-core or multifunctional designs?

It makes it easier to target testing to specific subsystems instead of the whole system at once.

Great observation, Student_1! Efficient targeting improves testing efficiency significantly.

Significance of TAM in Modern Designs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, let’s reflect on why effective test access mechanisms are crucial. What do you think?

They help ensure that complex systems are reliable and maintainable.

Absolutely, Student_2! Their significance continues to grow as designs become more intricate. Any final thoughts on TAM?

It sounds like they play a key role in both development and post-deployment.

Exactly! Test access mechanisms are foundational to the future of electronic testing.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section focuses on test access mechanisms (TAM) that improve testability in complex systems, particularly System-on-Chip (SoC) designs. It highlights the importance of Test Access Ports (TAP) and hierarchical TAM structures that allow for efficient testing and communication within multi-core and multi-functional designs.

Detailed

Test Access Mechanisms (TAM)

Test Access Mechanisms (TAM) are vital for improving the testability of complex electronic systems, especially in System-on-Chip (SoC) designs. They serve to streamline communication between testing equipment and the internal components of these systems, making testing processes more efficient.

Key Components of TAM

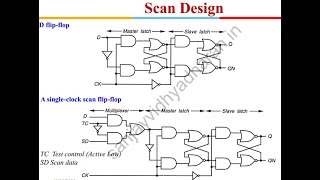

- Test Access Ports (TAP): The JTAG interface is a fundamental aspect of TAM, allowing access to internal signals and control over test execution. Recent advancements in TAP interfaces are focusing on handling high-speed, multifunctional systems with large-scale integration.

- Hierarchical TAM: This approach permits the application of testability features at various levels, from individual components to entire subsystems. Hierarchical TAMs enhance testing efficiency in multi-core and multifunctional designs by enabling targeted and structured testing strategies across various design levels.

Understanding and implementing effective TAMs are essential for the future of electronic systems, allowing engineers to ensure functionality, reliability, and maintainability of complex SoC designs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Test Access Mechanisms

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Effective test access mechanisms (TAM) are essential for improving testability, especially in complex SoC designs. TAMs enable efficient communication between the test equipment and the components inside the system.

Detailed Explanation

Test access mechanisms (TAM) are tools that facilitate communication between testing equipment and the components within a system, such as integrated circuits in a system-on-chip (SoC). They are crucial because as designs become more intricate, ensuring that each part can be quickly and accurately tested becomes increasingly challenging. Without effective TAM, tests might not reach all parts of the system, which could lead to untested components and potential failures.

Examples & Analogies

Think of TAM like the access roads to a large construction site. Just as these roads allow construction vehicles to reach different parts of the site efficiently, test access mechanisms allow testing equipment to communicate with various components of a complex electronic system.

Test Access Ports (TAP)

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Test Access Ports (TAP): The JTAG interface remains a critical tool for accessing internal signals and controlling test execution. Advanced TAP interfaces are being developed to handle high-speed, multi-functional systems with large-scale integration.

Detailed Explanation

The Test Access Port (TAP) is a significant feature in TAMs, particularly the Joint Test Action Group (JTAG) interface. JTAG allows engineers to gain internal access to the device’s circuits for testing purposes. This aspect is particularly vital for devices that perform many functions at high speeds. As technology advances, the design of TAP is evolving, making it capable of managing the complexity of modern devices better. This includes enhancements that allow for quicker and more efficient data transfer and control during testing.

Examples & Analogies

Imagine USB ports on various devices. Just like a USB port allows you to connect different devices and transfer data efficiently, a TAP functions similarly by giving engineers a connection point to access and test the internal workings of a circuit.

Hierarchical Test Access Mechanisms

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Hierarchical TAM: Hierarchical test access mechanisms allow testability features to be applied at different levels of the system, from individual components to entire subsystems. This hierarchical approach enables efficient testing of multi-core and multi-functional designs.

Detailed Explanation

Hierarchical test access mechanisms enable a structured way to implement testability features across different layers of a complex system. Instead of testing the system as a whole, which can be inefficient, this method allows for targeted testing at various levels—such as components, subsystems, or the entire architecture. This efficiency is crucial, especially for multi-core processors, where different cores can be tested independently to ensure each part functions correctly before integrating them.

Examples & Analogies

Consider a large apartment building where each floor has its own maintenance crew. Just as maintaining one floor at a time ensures that issues are addressed efficiently without interrupting the entire building, hierarchical TAM allows engineers to focus their testing efforts on specific sections of the system, making it easier to identify and rectify problems.

Key Concepts

-

Test Access Mechanism (TAM): A mechanism for testing communication within electronic systems.

-

Test Access Port (TAP): An interface enabling testing of components within a device.

-

Hierarchical TAM: A structured approach to apply testability features across system levels.

Examples & Applications

A typical JTAG connection allows engineers to access and control internal signals for effective debugging.

Hierarchical TAM implementation in a multi-core processor facilitates targeted testing of specific cores.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To test and check, we need a path, TAM and TAP will do the math!

Stories

Imagine a town where every building (subsystem) has its own door (TAP) leading to a central plaza (test equipment), making it easy to check and fix issues quickly.

Memory Tools

Remember TAP: Test Access Port - Think Access for testing Portals.

Acronyms

TAM

Test Access Mechanisms - Try Any Mechanism!

Flash Cards

Glossary

- Test Access Mechanism (TAM)

A system that facilitates communication between test equipment and the internal components of a design, enabling efficient testing.

- Test Access Port (TAP)

An interface that allows for access to internal signals and the control of test execution, commonly implemented through JTAG.

- Hierarchical TAM

An approach to testability that applies features at various levels, from individual components to entire subsystems.

- JTAG

Joint Test Action Group; a standard for using a serial communication interface for testing and debugging electronic systems.

Reference links

Supplementary resources to enhance your learning experience.