Design Rules

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Minimum Feature Size

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's begin with minimum feature size. This is essentially the smallest dimension that can be patterned on a semiconductor wafer. Can anyone tell me why this is important?

I think it's because it affects how small the circuits can be.

Exactly! The minimum feature size, like the 7nm node, is crucial because it determines the density and performance of the devices. The smaller the features, the more components can fit on a chip.

But what happens if we go beyond that minimum feature size?

Good question! Exceeding the minimum can lead to non-functional devices or performance degradation. That's why it's such a key rule. Remember, 'SMALL is FINE, but TOO SMALL is a CRIME!' This helps in recalling the balance needed.

Alignment Tolerance

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's discuss alignment tolerance. This defines how precisely we can align masks during the printing process. What do you think would happen if this tolerance is not maintained?

Would the devices become faulty?

Precisely! Misalignment can lead to defects that seriously impact device performance. An easy way to remember this is 'ALIGN TO SHINE!' Keep that in mind!

Are there specific standards for alignment tolerance?

Absolutely! Each technology node has specified tolerances. Maintaining them is critical for producing reliable devices.

Layer Stacking

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's look at layer stacking. Why is the compatibility of materials, specifically regarding CTE, so crucial in microfabrication?

It prevents stress issues in the layers when they expand or contract!

That's right! Mismatched CTE can lead to cracks or delamination. Always remember, 'MATCH OR PATCH OR YOU'RE IN A HATCH!' That's your way to remember this rule.

So, every layer in the process needs to be compatible, right?

Exactly! Layer compatibility is non-negotiable for reliable device performance. It's key to the overall design strategy.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section elaborates on vital design rules that govern the microfabrication process, emphasizing minimum feature sizes, alignment tolerances, and layer stacking compatibility. These rules are crucial for ensuring accurate manufacturing and device functionality.

Detailed

Detailed Summary

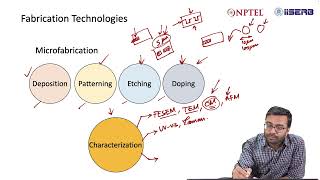

In this section titled Design Rules, we delve into the critical parameters that dictate the microfabrication processes for semiconductor devices. The main focus areas of this section include:

- Minimum Feature Size: This parameter sets the lithography resolution. For instance, contemporary technology might work with a 7nm node, which is pivotal in determining the smallest dimensions that can be reliably produced on the wafer.

- Alignment Tolerance: This aspect is crucial for ensuring that masks are accurately registered across various layers in the fabrication process. Proper alignment tolerance is necessary to avoid defects in multi-layer devices, making it a cornerstone of successful semiconductor manufacturing.

- Layer Stacking: The compatibility of materials in layer stacking is an important consideration. This means that the coefficient of thermal expansion (CTE) of the materials used must be compatible to prevent issues induced by thermal stress, which can lead to failures in device performance.

Understanding these design rules is integral to the chapters on microfabrication, allowing for precise planning and execution of semiconductor manufacturing where parameters are tightly controlled to enhance yield and performance.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Minimum Feature Size

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Minimum Feature Size: Dictates lithography resolution (e.g., 7nm node).

Detailed Explanation

The minimum feature size is the smallest dimension that can be reliably created on a semiconductor chip. It primarily affects the lithography resolution, which is the process used to transfer patterns onto the silicon wafer. For instance, advanced chips today operate at a minimum feature size of 7 nanometers (nm), meaning that the smallest components on the chip are just 7 billionths of a meter wide. This advancement allows for more transistors to fit onto a chip, enhancing performance and reducing power consumption.

Examples & Analogies

Imagine trying to paint a tiny detail on a model car. If your paintbrush is too thick, you won't be able to create fine details, just like a larger minimum feature size limits how tiny the components on a chip can be. The smaller the brush, the finer the details you can achieve.

Alignment Tolerance

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Alignment Tolerance: Mask-to-mask registration accuracy.

Detailed Explanation

Alignment tolerance refers to how accurately different layers of material can be aligned during the manufacturing process. Each layer of the semiconductor must align properly with the previous layer to ensure that the features match up correctly. Poor alignment can lead to defects such as short circuits or incomplete functionalities, making it crucial to maintain high registration accuracy between masks.

Examples & Analogies

Consider a jigsaw puzzle. If the pieces aren’t aligned correctly, the completed image will be distorted or unreadable. In semiconductor manufacturing, if the alignment isn’t precise between the layers (or 'pieces'), the final device won’t work correctly.

Layer Stacking

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Layer Stacking: Compatibility of materials (CTE matching).

Detailed Explanation

Layer stacking refers to the process of depositing multiple thin layers of materials on the semiconductor wafer. Compatibility of materials is crucial, particularly regarding their Coefficient of Thermal Expansion (CTE). If materials expand or contract at different rates when exposed to temperature changes, they can lead to stress cracks or delamination, which can damage the semiconductor device. Hence, selecting materials with matched thermal expansion properties is important for maintaining structural integrity.

Examples & Analogies

Think about stacking different sizes of rubber bands. If one is too tight or too loose compared to the others, it can cause the whole stack to collapse or snap. In the same way, if the layers in semiconductor devices don’t match well thermally, it can cause serious issues.

Key Concepts

-

Minimum Feature Size: Determines the smallest viable circuit dimensions affecting device density and performance.

-

Alignment Tolerance: Defines how accurately masks are positioned, critical to avoid defects.

-

Layer Stacking: Focuses on the compatibility of materials in multi-layer structures to ensure structural integrity.

-

Coefficient of Thermal Expansion (CTE): Critical for materials used in layer stacks to prevent stress-related issues.

Examples & Applications

In modern microelectronics, a minimum feature size of 7nm allows for denser packing of transistors on CPUs, leading to increased performance.

Mismatched CTE in layer stacking can cause cracks in the silicon layer during temperature changes, risking device functionality.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Minimum size must align, or the device may decline!

Stories

Imagine building a house where every brick must line up perfectly; if one is misaligned, the entire structure might crumble. This illustrates the importance of alignment tolerance in semiconductor layers.

Memory Tools

MAL: Minimum feature size, Alignment tolerance, Layer stacking – Remember MAL to capture key design rules!

Acronyms

CALM

Compatibility

Alignment

Layer

Minimum – to remember the design priorities in microfabrication.

Flash Cards

Glossary

- Minimum Feature Size

The smallest dimension that can be reliably created using lithography in semiconductor fabrication.

- Alignment Tolerance

The permissible deviation of mask positioning during lithography, critical for device functionality.

- Layer Stacking

The arrangement of different material layers on a substrate, requiring compatibility in their physical properties.

- Coefficient of Thermal Expansion (CTE)

A material's tendency to expand or contract with changes in temperature, significant for layer compatibility.

Reference links

Supplementary resources to enhance your learning experience.