Implementation Case Study

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Starting with the p-type silicon wafer

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's begin by talking about the first step in our MOSFET process: selecting the substrate. Why do you think we start with a p-type silicon wafer?

Is it because of its electrical properties?

Exactly! P-type silicon has holes that can facilitate charge transport. This is crucial for our MOSFET to function effectively.

So, does it affect the performance of the whole device?

Yes, the choice of substrate affects the yield and performance. Remember the acronym 'S.P.E.A.R': Substrate Performance Equals Application Reliability!

That's a great way to remember it!

Growing the Gate Oxide

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, we need to grow the gate oxide. Why is this step necessary?

I think it insulates the gate from the channel?

Correct! A 4nm gate oxide ensures effective electrostatic control of the channel. Let’s remember 'G.O.A.T' - Gate Oxide's Amazing Transition!

How does dry oxygen help in this process?

Great question! Dry O₂ provides the right environment for forming a thin and uniform oxide layer. It's crucial for device reliability.

Patterning with I-line Lithography

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s discuss the patterning step where we use i-line lithography. Why is patterning crucial?

It creates the structures we need on the wafer.

Exactly! We are defining critical features that will ultimately affect the MOSFET's functionality. Remember 'P.A.T.E' - Patterns Are The Essence!

What happens if the patterning is not accurate?

Inaccurate patterning can lead to defects, reducing yield and performance. Precision is key!

Implanting N+ Regions

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s look at the doping process for creating the n+ regions. Why do we use arsenic ions?

I think they donate electrons to the silicon?

That's right! Arsenic is a donor that increases the carrier concentration. Let’s keep in mind 'D.O.N.A.T.E' - Doping Offers New Attributes To Electrons!

What about the energy and dose used during implantation?

Good point! The energy level (50 keV) and dose (5e15/cm²) are crucial for achieving the desired dopant profile.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

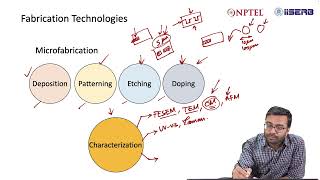

This section details a practical example of designing a 180nm MOSFET process, outlining key steps such as starting with a p-type silicon wafer, growing a gate oxide, using lithography for patterning, and implanting dopants for n+ regions.

Detailed

Implementation Case Study

This section presents a practical implementation case study focused on designing a 180nm MOSFET process. The process begins with the selection of a substrate, specifically a p-type silicon wafer, which sets the foundation for the subsequent operations. Key steps include:

- Growing the Gate Oxide: A critical step where a 4nm layer of gate oxide is grown using dry oxygen (O₂) to ensure proper electrical insulation and performance of the MOSFET.

- Patterning: Utilizing i-line lithography for precisely defining patterns on the wafer is essential to create the necessary features on the semiconductor.

- Doping: The n+ regions are formed by implanting arsenic ions (As⁺) at a specific energy level (50 keV) and dosage (5e15/cm²), which is crucial for determining the electrical characteristics of the device.

All these steps contribute toward the overall quality and functionality of the MOSFET device, highlighting the importance of meticulous planning and execution in microfabrication.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Project Overview

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Design a 180nm MOSFET process:

Detailed Explanation

This chunk introduces the case study where we design a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) process using a 180nm technology node. The reference to '180nm' indicates the smallest half-pitch of contactable features in the manufacturing process. This technology node was commonly used in the early 2000s and is useful for teaching fundamental concepts in semiconductor fabrication.

Examples & Analogies

Think of designing a 180nm MOSFET as trying to build a small electrical circuit on a miniature circuit board, where every component must be carefully placed and connected to work correctly.

Starting Material

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Start with p-type Si wafer

Detailed Explanation

The first step in this process is to use a p-type silicon wafer. Silicon is the most widely used material in semiconductor devices, and the 'p-type' refers to the doping type where holes (positive charge carriers) are the majority carriers. This choice of starting material is crucial as it sets the foundation for how the MOSFET will function.

Examples & Analogies

It's similar to using a specific type of bread for a sandwich; the kind you choose will affect the flavor and structure of the final product.

Gate Oxide Growth

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Grow 4nm gate oxide (dry O₂)

Detailed Explanation

In this step, a thin layer of gate oxide is created on top of the silicon wafer using dry oxygen. The thickness of this oxide layer is critical; at 4nm, it's thin enough to allow for efficient operation of the MOSFET while still providing the necessary insulation. This oxide acts as a dielectric material, allowing the MOSFET to control current without them shorting together.

Examples & Analogies

Think of the gate oxide as a delicate layer of frosting on a cake—too thick and it becomes cloying, but just right, it enhances the overall experience without overpowering the base layer.

Lithography Patterning

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Pattern with i-line lithography

Detailed Explanation

After the gate oxide is grown, the next step is to use i-line lithography to pattern the features onto the silicon wafer. Lithography is a process that uses light to transfer a geometric pattern from a photomask to a light-sensitive chemical photoresist on the wafer. The term 'i-line' refers to a specific wavelength of light that is commonly used in photolithography. This process is essential for defining smaller and more intricate features on the MOSFET.

Examples & Analogies

Imagine using a stencil to paint a design on a wall. The stencil allows you to create sharp and precise patterns, just as lithography helps define the tiny structures necessary for the MOSFET to function properly.

Doping Process

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Implant As⁺ for n+ regions (50keV, 5e15/cm² dose)

Detailed Explanation

In this step, arsenic ions (As⁺) are implanted into specific regions of the silicon wafer to create n+ regions, which will act as the source and drain of the MOSFET. The energy of 50keV (kiloelectron volts) and a dose of 5e15 atoms per cm² are carefully chosen parameters that determine how deeply and densely the arsenic ions penetrate into the silicon. This process modifies the electrical properties of the silicon, allowing it to conduct electricity in specific regions.

Examples & Analogies

This is much like planting seeds at specific depths and densities in a garden. Too shallow, and they fail to grow; too deep, and they may not sprout at all. The careful balance ensures that the device will work as intended.

Key Concepts

-

MOSFET: A device that functions as a switch or amplifier, critical in modern electronics.

-

p-type Silicon: The type of silicon used that contains holes as majority carriers.

-

Gate Oxide: An insulating layer essential for controlling the flow of current in a transistor.

-

I-line Lithography: A method used for patterning semiconductor wafers.

-

Doping: The process of introducing impurities to modulate the electrical properties of semiconductors.

Examples & Applications

In the MOSFET process, using a p-type silicon wafer is crucial because it minimizes electron recombination.

The use of arsenic (As⁺) for doping creates n+ regions that facilitate electron flow, enhancing current capability in the device.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When starting my MOSFET, p-type's the best bet!

Stories

Imagine a tiny city where silicon is built, with waste materials carefully chipped away until the perfect structures emerge, just like precise electron pathways.

Memory Tools

S.P.E.A.R - Substrate Performance Equals Application Reliability.

Acronyms

G.O.A.T - Gate Oxide's Amazing Transition!

Flash Cards

Glossary

- MOSFET

A type of field-effect transistor that is commonly used for switching and amplifying electronic signals.

- ptype Silicon

Silicon that has been doped with acceptor impurities, resulting in a higher concentration of holes.

- Gate Oxide

A thin layer of insulating material that separates the gate from the channel in a MOSFET.

- Iline Lithography

A photolithography process that uses light with a wavelength of 365 nm.

- Doping

The process of adding impurities to semiconductor materials to change their electrical properties.

Reference links

Supplementary resources to enhance your learning experience.