Challenges in Verification

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Design Size Challenges

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's begin by discussing the first challenge: design size. As VLSI designs grow, the number of possible states increases dramatically. Can anyone explain why this makes verification challenging?

I think it's because with more states, there's more potential for bugs or issues to exist, which we need to check.

Exactly! The larger the design, the more behaviors we need to verify. This exponential growth makes comprehensive verification impractical. We use terms like 'state explosion' to describe this phenomenon. Can anyone give me a brief summary of what state explosion means?

State explosion refers to the rapid growth in the number of states that need to be explored during verification as the design becomes more complex.

Great summary! Remember, managing this complexity is crucial, leading us to develop more sophisticated verification methods.

Timing Analysis Complexity

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s talk about timing analysis. Why is verifying timing constraints becoming more complex in modern designs?

I think it's because designs often have multiple clock domains and operate at high frequencies?

Correct! Multiple clock domains introduce complexity as we need to ensure that signals arrive at the correct time across different parts of the circuit. This adds to the computational cost and extends verification time. Can someone suggest a technique we use to deal with timing verification?

Static Timing Analysis helps to verify timing constraints without simulation.

Exactly, STA is essential for checking timing paths effectively without needing exhaustive simulations. Any questions about timing constraints or their implications?

Multilayer Design Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's wrap up with multilayer designs. What issues do you think arise from having multiple layers of interconnects?

Multilayer designs complicate routing and verification since we need to ensure all layers work together without interference.

Absolutely! We need sophisticated algorithms to ensure interactions between layers are verified correctly. Can anyone name a verification technique that could help in this scenario?

Maybe we could use formal verification to ensure that the properties of the multilayer design are satisfied?

That's a valid point! Formal verification can help us rigorously prove that designs behave as intended. Remember, the goal is to ensure that with each added layer, we maintain functionality without errors.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

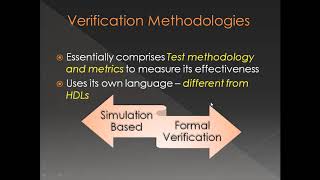

This section outlines the key challenges faced in the verification of VLSI designs, including the growing size and complexity of designs, the difficulties of timing analysis under varying clock domains, and the complications introduced with multilayer designs. These obstacles require sophisticated verification algorithms and extensive resources to address effectively.

Detailed

Challenges in Verification

As VLSI designs increase in complexity and size, the verification process becomes more challenging and resource-intensive. The key challenges include:

- Design Size: The larger the design, the more difficult it is to verify every potential behavior due to the exponential increase in the number of states that need to be checked.

- Complexity of Timing Analysis: Analyzing timing constraints becomes increasingly difficult with multiple clock domains and high-frequency designs, leading to high computational costs and longer verification times.

- Verification of Multilayer Designs: Advanced designs often involve multilayer interconnects and intricate routing, necessitating sophisticated verification methods to ensure that all layers function correctly together. These challenges underline the need for continual advancements in verification methodologies and algorithms, to ensure reliability and correctness in modern VLSI designs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Design Size

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Design Size: The larger the design, the more difficult it is to verify every possible behavior.

Detailed Explanation

As circuit designs become larger and more complex, the task of verifying them becomes increasingly challenging. Each unique configuration or behavior of the design must be tested to ensure functionality, which requires significant time and resources. Larger designs may contain a tremendous number of possible states and transitions, making it practically impossible to check them all exhaustively. This means that verification methods need to be efficient and capable of narrowing down the possible behaviors that need to be examined.

Examples & Analogies

Imagine trying to find a specific book in a vast library with millions of books. The bigger the library, the more time-consuming it would be to search for just one book unless you have a way to narrow it down, like a catalog system. In circuit design, we use verification algorithms and techniques to reduce the complexity of our search for errors in large designs.

Complexity of Timing Analysis

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Complexity of Timing Analysis: With multiple clock domains and high-frequency circuits, verifying timing constraints can become computationally expensive and time-consuming.

Detailed Explanation

Timing analysis is a crucial part of VLSI verification to ensure that signals propagate correctly and all timing requirements are met. In modern designs, circuits may operate under multiple clock domains, meaning different sections of a chip might utilize different clock frequencies. This added complexity increases the workload for timing verification, as more possibilities need to be analyzed for setup and hold times, propagation delays, and other timing constraints. As clock frequencies increase, the number of timing paths to verify expands exponentially, making the verification process more resource-intensive and time-consuming.

Examples & Analogies

Think of an orchestra where different instruments play at different tempos. The conductor must ensure that each group stays in time without clashing. In circuit design, having multiple clock domains is like managing an orchestra with various tempos, making it challenging to ensure everything harmonizes perfectly at high speeds.

Verification of Multilayer Designs

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Verification of Multilayer Designs: Advanced designs with multiple layers of interconnects and complex routing require sophisticated verification algorithms to ensure that all layers work correctly together.

Detailed Explanation

Complex VLSI designs often consist of multiple layers that include various interconnections between components. These multilayer designs can pose verification challenges because issues in one layer can affect the entire design's functionality. Sophisticated verification algorithms are needed to assess interactions between layers, ensuring that all connections are correctly established and that signals can propagate through different layers without interference or loss of information. Without effective algorithms to verify these multilayer designs, errors may go undetected, leading to faulty circuit designs.

Examples & Analogies

Imagine constructing a multi-story building where each floor has to connect perfectly with the one above and below it, with elevators and plumbing running seamlessly through the structure. If one floor’s construction is flawed, it could impact the entire building. In VLSI, verifying multilayer designs requires careful checks to ensure that each layer integrates and functions properly with others, just like ensuring all floors of a building are correctly built to work together.

Key Concepts

-

Design Size: Larger designs lead to exponentially more states that complicate verification.

-

Timing Analysis: The presence of multiple clock domains complicates checking timing constraints.

-

Multilayer Verification: Additional layers in design complicate interaction verification.

Examples & Applications

State explosion impacts verification by increasing the complexity of ensuring all conditions are met in chip designs.

Static Timing Analysis is used in practice to minimize potential timing violations in high-frequency design scenarios.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

For designs that are large and wide, state explosion you cannot hide.

Stories

Imagine a bridge that needs to be built across multiple layers of water; each layer represents a circuit layer that must stay connected without leaking information—this is like multilayer design verification.

Memory Tools

Remember the acronym SLIME for verification challenges: Size, Layers, Interconnections, Multi-domain clock, Exponential states.

Acronyms

The acronym TIME for memory can aid in recalling Timing Analysis, Interlayer complexity, Multilayer challenges, and Exponential growth issues.

Flash Cards

Glossary

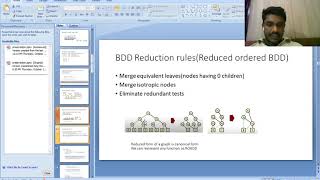

- State Explosion

A phenomenon where the number of states to be verified increases exponentially with the complexity of the design.

- Static Timing Analysis (STA)

A method for verifying timing constraints without simulation by analyzing delays in a circuit.

- Verification

The process of checking that a system meets specifications and requirements.

- Multilayer Design

A VLSI design that includes multiple layers of materials for interconnections and routing.

Reference links

Supplementary resources to enhance your learning experience.