Timing Verification in VLSI

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Timing Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss timing verification in VLSI. Why do you think it's so important?

I think it's about making sure the circuit runs fast enough.

Exactly! Timing verification ensures our designs meet timing constraints like setup and hold times. Can anyone explain what setup time means?

Isn't it the time before the clock signal when the input needs to be stable?

Correct! Setup time is crucial for the proper functioning of flip-flops. Remember: 'Settle before the clock's petal.'

Key Timing Parameters

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about another timing parameter—hold time. Who can tell me what that is?

It's the time after the clock edge that the input needs to remain stable, right?

Yes! Hold time ensures data is latched correctly. Now, why might clock skew be a concern?

If the clock arrives at different times, then some parts of the circuit might not function properly.

Exactly! Clock skew can lead to critical failures in synchronization. Remember: 'Skew is not few; it’s something to view!'

Methods for Timing Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's explore methods of timing verification. Who's heard of Static Timing Analysis, or STA?

Isn't that the method that checks timing without simulating the circuit?

Exactly! STA assesses all paths for delays to ensure timing rules are not violated. Now, what about Clock Tree Analysis?

That's where you ensure the clock signal is distributed evenly, right?

Right! Minimizing clock skew is essential for synchronous operation. Remember the acronym 'STA' - Synchronous Timing Assurance.

Path-Based Timing Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's dive into Path-Based Timing Verification. What is its significance?

It checks the critical paths to make sure they can meet timing required for performance.

Correct! Identifying these paths helps focus optimization efforts. Who can tell me what the critical path is?

It's the longest path in the circuit that determines the maximum clock speed.

Exactly, nice work! Remember: 'Critical paths rule the timing duel.'

Consolidating Key Points

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To summarise, timing verification ensures that VLSI designs can operate correctly at the intended clock speed without timing violations. What are the three main aspects we focus on?

Setup time, hold time, and clock skew!

Great! And what are some verification methods we've discussed?

Static Timing Analysis, Clock Tree Analysis, and Path-Based Timing Verification.

Well done, everyone! Remember the key phrases we used to keep these concepts in mind!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the critical aspects of timing verification which involve ensuring the design meets setup and hold times, clock skew, and utilizes methods such as static timing analysis and clock tree analysis to verify timing constraints.

Detailed

Timing Verification in VLSI

Timing verification is a crucial process in VLSI design, primarily aimed at ensuring that a digital circuit operates at the desired speed without experiencing timing violations such as setup or hold times. Key aspects of timing verification include:

- Setup Time: The minimum time before the clock edge during which the input signal must be stable for proper latch behavior.

- Hold Time: The minimum time after the clock edge that the input signal must remain stable to guarantee correct operation.

- Clock Skew: The discrepancy in arrival times of the clock signal at different flip-flops, which can lead to timing issues.

To accurately verify timing constraints, various methods are employed, such as:

- Static Timing Analysis (STA): A non-simulation method that checks all signal paths for timing violations based on delay and timing library data without needing to simulate every scenario.

- Clock Tree Analysis: Focuses on ensuring that the distribution of the clock signal within the design minimizes clock skew and ensures synchronous operation of all flip-flops.

- Path-Based Timing Verification: This involves analyzing the significant signal paths to ensure critical paths meet performance requirements, essential in high-speed designs.

Understanding these aspects is vital for confirming that VLSI designs not only function as expected but also operate reliably under specified timing parameters, reflecting the critical nature of timing verification in the design flow.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Timing Verification

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing verification is essential to ensure that the design operates at the intended speed and meets the timing constraints. The goal is to verify that the design can operate correctly at the desired clock frequency without encountering setup or hold violations.

Detailed Explanation

Timing verification is a critical process in the design of digital circuits. It checks whether the circuit can function correctly at the specified clock speed. Every digital circuit relies on precise timing to perform operations accurately. The primary purpose of timing verification is to ensure that the circuit's performance meets defined constraints, specifically watching for two critical types of timing violations: setup time and hold time. Setup time is the interval before a clock pulse when inputs must be stable to ensure proper operation, and hold time is the interval after the clock pulse when inputs must remain unchanged.

Examples & Analogies

Think of a relay race where each runner passes the baton to the next. If the baton is passed too early or too late, the next runner will not be prepared, leading to a potential loss of race time. Similarly, in timing verification, if data inputs change too close to the clock signal, the circuit may misinterpret the values, leading to incorrect operations.

Key Timing Constraints

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Key timing-related aspects to verify include:

● Setup Time: The time before the clock edge when the input to a flip-flop must be stable.

● Hold Time: The time after the clock edge during which the input must remain stable.

● Clock Skew: The difference in arrival times of the clock signal at different flip-flops.

Detailed Explanation

In timing verification, understanding key constraints is fundamental for ensuring reliable circuit operation. Setup time ensures inputs are stable before a clock edge; if inputs fluctuate during this window, the flip-flop may read incorrect values. Hold time, conversely, requires stability after the clock edge; fluctuations here can also lead to inaccuracies. Clock skew is another critical aspect, referring to variations in clock signal arrival times. As digital designs often use multiple flip-flops, any discrepancies in clock arrival can destabilize the operation of interconnected circuits.

Examples & Analogies

Imagine a group of students starting a race. If some students start running before the signal to go is given (setup time violation), they'll likely fall behind when the official start is called because they're not ready. Similarly, if some students stop running too soon after the signal (hold time violation), they may not finish strong. Lastly, if some students receive the start signal later than others (clock skew), they’ll be out of sync, leading to chaos in the race.

Methods for Timing Verification

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

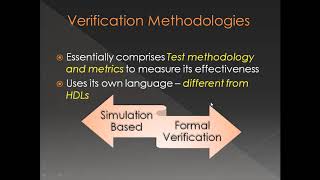

7.3.1 Timing Verification Methods

● Static Timing Analysis (STA): STA is a method used to verify whether the timing constraints of the design are met without the need for simulation. It checks the delay of all signal paths in the design and ensures that there are no timing violations, such as setup or hold violations. STA operates by analyzing the timing of all paths in the design using the timing library and propagation delay information.

● Clock Tree Analysis: This is part of timing verification where the clock tree, which distributes the clock signal across the design, is analyzed to ensure that all flip-flops receive the clock signal at the correct time. The goal is to minimize clock skew and ensure that the clock signal arrives simultaneously at all flip-flops.

● Path-Based Timing Verification: In path-based verification, the delay of critical paths is checked to ensure that they meet timing requirements. This is particularly important for high-speed designs where the timing of specific paths can determine the performance of the entire circuit.

Detailed Explanation

Timing verification can be achieved through several methods: Static Timing Analysis (STA) allows designers to evaluate timing constraints mathematically without simulating all inputs. It systematically examines the delays along all possible signal paths to identify violations. Clock Tree Analysis ensures that the clock signal reaches all flip-flops at the same time, addressing potential clock skew. Path-Based Timing Verification focuses on specific critical paths, determining if they satisfy timing requirements to ensure high-speed operation. By using these methods collaboratively, design teams can ensure maximal performance and reliability.

Examples & Analogies

Consider an assembly line where different workers must complete their tasks in a specific order to maintain production efficiency. If one worker (flip-flop) has to wait too long for the materials (clock signal), it slows down the entire process. STA is like a manager analyzing the time each worker is taking and ensuring no one is delayed beyond the acceptable limits. Clock Tree Analysis ensures that every worker starts their task at the same moment. Path-Based Timing Verification is like inspecting the most crucial part of the assembly line to make sure it runs smoothly.

Algorithms for Timing Analysis

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

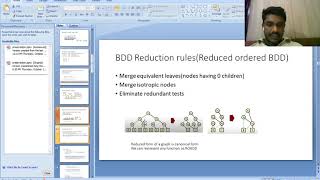

7.3.2 Verification Algorithms for Timing Analysis

● Delay Propagation Algorithms: These algorithms calculate the delay of signals through various paths in the design, from input to output. The most commonly used method is the Slack Analysis algorithm, which compares the actual delay against the required delay to ensure that timing constraints are met.

● Critical Path Analysis: The critical path is the longest path in the circuit that determines the maximum clock speed. Critical path analysis identifies the most timing-critical sections of the design, enabling designers to focus optimization efforts on those paths.

● Retiming: Retiming involves adjusting the positions of flip-flops to optimize the timing of the design. The goal is to reduce the delay along critical paths by redistributing the registers while maintaining the design’s functionality.

Detailed Explanation

There are specialized algorithms that aid in timing analysis: Delay Propagation Algorithms such as Slack Analysis help determine how delays affect signal integrity by comparing actual signal delays to required constraints. Critical Path Analysis identifies the longest delay in the circuit, which dictates the maximum frequency at which the design can operate. Understanding critical paths allows designers to make strategic optimizations. Retiming allows adjustments of flip-flop locations to effectively manage timing without compromising circuit functionality, ensuring that performance remains optimal.

Examples & Analogies

Imagine a team working on a project where each member has specific tasks that depend on others’ completions. Delay Propagation is like tracking how long each task takes as a whole. Critical Path Analysis is identifying the task that takes the longest, which decides when the project can be completed. Finally, Retiming can be likened to redistributing tasks among team members to ensure no single person is overloaded, enhancing overall project efficiency without sacrificing quality.

Key Concepts

-

Timing Verification: Ensures VLSI designs operate correctly at specified clock speeds without timing violations.

-

Setup Time: The time before the clock edge requiring input stability.

-

Hold Time: The time after the clock edge requiring input stability.

-

Clock Skew: Variation in clock signal arrival times affecting circuit behavior.

-

Static Timing Analysis (STA): Non-simulation method for verifying timing constraints.

-

Clock Tree Analysis: Process for analyzing clock distribution to minimize skew.

-

Path-Based Timing Verification: Method for checking critical paths to meet timing requirements.

Examples & Applications

Example 1: A design with a setup time violation may fail to register the correct input before the next clock edge occurs.

Example 2: A clock skew of 1 ns could result in one flip-flop capturing data too late compared to another, potentially causing logic errors.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Setup must stay, hold is the way, timing must play for VLSI's stay.

Stories

Imagine a race where circuits are runners. Each runner has their own start signal (the clock). If some runners get their signal too late (clock skew) or too early (setup time), the race won't happen correctly!

Memory Tools

Remember 'SHC', which stands for Setup, Hold, and Clock skew to check for timing.

Acronyms

STA for Static Timing Analysis, a key verification tool in our toolkit.

Flash Cards

Glossary

- Setup Time

The minimum time before a clock edge when the input to a flip-flop must be stable.

- Hold Time

The minimum time after a clock edge during which the input must remain stable.

- Clock Skew

The difference in arrival times of the clock signal at different flip-flops.

- Static Timing Analysis (STA)

A method used to verify timing constraints of a design without simulation.

- Clock Tree Analysis

Analysis of the clock distribution network to reduce clock skew.

- PathBased Timing Verification

Verification of critical paths to ensure they meet performance timing requirements.

Reference links

Supplementary resources to enhance your learning experience.