Introduction to VLSI Verification

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we will explore VLSI verification, which is crucial in ensuring that our designs work as intended. Can anyone tell me why verification is so important?

It's to make sure the circuit functions correctly, right?

Exactly! Verification is critical to confirm that the design meets its functional and timing specifications. In VLSI, we focus on two main types of verification: functional and timing. Can someone summarize what functional verification aims to achieve?

It checks if the design behaves correctly according to the specifications!

Great! And timing verification ensures that designs operate correctly at the desired clock speeds, maintaining setup and hold times. Remember the acronym FPT for 'Functional, Performance, Timing'! It’s key to our discussion today.

Functional Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we have an understanding of verification, let’s focus on functional verification. What methods do we use for this?

We can use simulation and testbenches!

Exactly! Simulation helps us verify behavior at different abstraction levels like RTL or gate-level. What do you think is a testbench in this context?

It's a setup that applies inputs to the design and checks the outputs, right?

Yes! Also, we can generate random input vectors using random simulation. This coverage metric helps in identifying unusual behavior. Remember our mnemonic 'SRFT' for Simulation, Random, Functional, Testbench! It’s easier to remember like that.

Timing Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s shift our focus to timing verification. Why is timing verification important in VLSI design?

It ensures our design can run at the intended clock speed without issues!

Correct! Timing verification checks elements like setup time and hold time. Can anyone explain what static timing analysis does?

STA analyzes signal delays without simulation to ensure timing constraints are met.

Exactly! It’s crucial for avoiding timing violations. Remember, timing is everything in VLSI; we want our circuits to work harmoniously with timing constraints and avoid issues like clock skew.

Challenges in Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

As we learn about VLSI verification, let's discuss some challenges. What do you think makes verification difficult?

Design size and complexity make it hard to verify everything!

Right! Larger designs can have numerous potential behaviors. Also, what about timing analysis complexity?

With high-frequency circuits and multiple clock domains, it takes a lot of effort and resources!

Precise! And multilayer designs require advanced algorithms. It's vital to have effective verification strategies as the complexity of VLSI systems continues to rise. Remembering the acronym 'CLEVER' for Complexity, Layer verification, Efficient analysis, is helpful.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the significance of verification in VLSI design, introducing key types such as functional and timing verification. We discuss how verification algorithms validate circuit behavior and ensure compliance with timing constraints, highlighting the challenges posed by increasing design complexity.

Detailed

Introduction to VLSI Verification

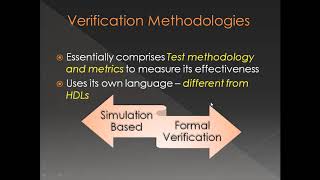

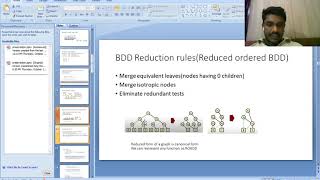

Verification plays a crucial role in the VLSI design flow, ensuring that designs meet both functional and timing specifications. As VLSI projects grow in complexity, the verification process has emerged as one of the most demanding challenges. The primary goal of verification is to validate that the design functions correctly and adheres to timing constraints, such as setup time, hold time, and clock frequency. This section categorizes verification into two main types: functional verification, which checks if the design behaves as intended, and timing verification, which ensures that the design meets speed requirements. Functional verification methods include simulation at various abstraction levels, such as RTL and gate-level simulations, while timing verification focuses on analyzing setup times and hold times. The growing intricacies of VLSI designs underscore the necessity of effective verification algorithms to ensure reliability and performance.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Verification in VLSI Design

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Verification is a critical step in the VLSI design flow, ensuring that the design meets its functional and timing specifications. Verification algorithms are used to validate that the circuit behaves as intended and that it meets the required timing constraints.

Detailed Explanation

Verification is the process of checking if a design works as it should. In the context of Very Large Scale Integration (VLSI), this means making sure that the electronic circuit functions correctly and adheres to timing specifications, which dictate how fast the circuit can operate. This step is crucial because even a small error in design can lead to significant failures in the final product. Thus, verification algorithms help engineers ensure reliability and performance.

Examples & Analogies

Think of verification like proofreading a book before it is published. Just as an editor makes sure that all the content is correct and errors are fixed to ensure that readers have a great experience, verification ensures that an electronic design meets all specifications and functions well.

Challenges in VLSI Verification

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As VLSI designs become increasingly complex, verification has become one of the most time-consuming and challenging aspects of the design process. This chapter provides an in-depth study of the functional and timing verification algorithms used in VLSI design.

Detailed Explanation

The complexity of modern VLSI designs can create significant challenges for verification. With more components and intricate functionalities, ensuring that every part works as intended becomes a daunting task. This chapter will explore both functional verification, which checks design behavior, and timing verification, which ensures all signals meet timing requirements. Understanding these algorithms is essential for dealing with the complexity of current VLSI systems.

Examples & Analogies

Imagine a busy airport with multiple flights and delays. Just as air traffic controllers need to ensure that all planes take off and land safely despite the hectic environment, engineers must carefully verify that all components in a VLSI design work together correctly, even as designs grow more complex.

Types of Verification

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

There are two primary types of verification: Functional Verification and Timing Verification.

Detailed Explanation

Functional verification ensures that the design behaves according to specified requirements. This includes checking if the circuit performs all intended operations correctly. Timing verification, on the other hand, focuses on whether the design meets timing constraints, such as data stability around clock signals. Both types of verification are essential for successful VLSI design.

Examples & Analogies

Think of a restaurant. Functional verification is like ensuring that the dishes on the menu are cooked correctly and taste good, while timing verification is making sure that each dish is served promptly, between the time the order is placed and when it arrives at the table.

Key Concepts

-

Verification: Critical for validating design functionality and timing.

-

Functional Verification: Ensures designs work as intended.

-

Timing Verification: Validates design timing constraints.

-

Testbench: Simulates input and output validation.

-

Static Timing Analysis: Verifies timing without simulation.

Examples & Applications

An example of functional verification would be using a testbench to simulate a digital circuit and confirm its outputs match expected results for given inputs.

Static timing analysis can prevent design errors by checking setup and hold times without needing to run a simulation.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In VLSI design, verification’s key, ensuring functionality is what we seek.

Stories

Imagine a smart circuit trying to perform a task. Verification checks its actions, ensuring no detail is askew, much like a teacher reviewing homework.

Memory Tools

Remember 'FPT' for Functional, Performance, Timing – the pillars of VLSI verification!

Acronyms

Use 'CLEVER' to recall Complexity, Layer verification, Efficient analysis for verification strategies.

Flash Cards

Glossary

- Verification

The process of validating that a design meets its functional and timing specifications.

- Functional Verification

A type of verification that ensures the design behaves correctly according to specifications.

- Timing Verification

A form of verification that ensures the design meets required timing constraints.

- Testbench

A simulated environment used to apply inputs to a design and validate outputs.

- Static Timing Analysis

A method for verifying timing constraints by analyzing delays without simulation.

Reference links

Supplementary resources to enhance your learning experience.