Functional Verification in VLSI

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Functional Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're exploring Functional Verification in VLSI. Can anyone tell me why functional verification is important?

I think it's to make sure the circuit works as intended.

Exactly! Functional verification ensures designs behave as expected under various conditions. What are some methods we might use for this?

We could use simulations and maybe formal verification?

What do you mean by formal verification, Teacher?

Good question, Student_3! Formal verification uses mathematical proofs to ensure the design meets its specifications. Let's remember this as 'Mathematics of Verification' — it gives a structural approach to validate functionality.

Methods of Functional Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about the methods for functional verification. Who can tell me the different levels of simulation?

We have RTL simulation, gate-level simulation, and post-layout simulation, right?

That's correct! Let's remember — 'RTL, Gate, and Post-Layout' — each plays a crucial role. What’s the difference between them?

RTL simulates at a high level, while gate-level checks after synthesis, and post-layout verifies the actual design once it's laid out.

Excellent! Recognizing the progression from RTL down to post-layout is vital in understanding how verification works. What about formal methods? Who can name one?

Model checking?

Yes! Model checking helps exhaustively verify properties of the design. Remember, 'Model Checking = Exhaustive Checks'.

The Role of Testbenches and Random Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's discuss testbenches. What role do they play in functional verification?

They apply input signals and check the outputs, right?

Exactly! Think of a testbench as a controlled environment for your circuit. What about random simulation? How does that help?

It checks how the circuit behaves under various conditions!

Spot on! It can help uncover edge cases. So remember, 'Testbenches = Controlled Testing, Random = Wide Exploration'.

Review and Summary of Functional Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, why is functional verification vital again?

To ensure the circuit meets its specifications!

Great! Let's summarize the methods we discussed. Can anyone list them?

We talked about simulation, formal verification, testbenches, and random simulation.

Correct! Each technique ultimately focuses on confirming that our VLSI design operates correctly under all intended conditions. Remember: 'Verify to Certify'.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses functional verification in VLSI design, emphasizing its significance in ensuring correct circuit behavior according to specifications. Key methods include simulation at different abstraction levels, formal verification techniques, and the use of testbenches and random simulations.

Detailed

Functional Verification in VLSI

Functional verification is an essential phase in the VLSI design process where the aim is to ensure that the design performs according to the defined functionality in its specifications. This process checks that all operations of the circuit behave correctly under various operating conditions. To achieve this, functional verification employs several methods, including different levels of simulation, formal verification, testbenches, and random simulation.

Key Methods of Functional Verification

Simulation

Simulation is often the first step in verifying functionality, where the design is run using input vectors to check the output behavior. Various levels of simulation include:

- RTL Simulation: Validates the Register Transfer Level (RTL) description with testbenches.

- Gate-Level Simulation: Checks the synthesized gate-level netlist post-synthesis for correctness.

- Post-Layout Simulation: Verifies the functionality after the physical layout and routing are completed.

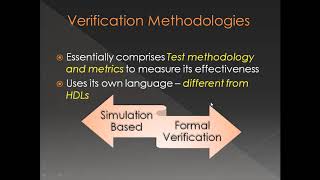

Formal Verification

This method employs mathematical proofs to ensure the design complies with its specifications. Techniques involved are:

- Model Checking: Automatically verifies that the design meets certain properties by exhaustively examining all states.

- Equivalence Checking: Confirms that the RTL design and its gate-level counterpart are functionally identical.

- Property Checking: Ensures specific properties related to the design's functionality hold true.

Testbenches

Testbenches facilitate simulation by applying input stimuli to the design and observing the corresponding outputs through different scenarios, thus assuring functional accuracy across various tests.

Random Simulation

This method generates random input vectors to explore the design's behavior widely, potentially identifying edge cases that conventional testbenches may miss.

Functional verification significantly helps in addressing the complexity of modern VLSI designs and ensures that they perform reliably.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of Functional Verification

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Functional verification aims to ensure that the design meets the intended functionality by checking that all operations of the circuit behave correctly. It involves simulating the design to verify that it performs as expected under various operating conditions.

Detailed Explanation

Functional verification is a critical step in VLSI design. It ensures that the circuit operates as it should according to its specifications. This process is primarily done through simulation, where the intended operations of the design are tested to check if everything functions correctly in different scenarios. For instance, when you press a button, you expect the screen to light up; functional verification ensures that the design operates just as expected under diverse conditions.

Examples & Analogies

Think of functional verification like a chef tasting a dish while cooking. Just as a chef samples food to ensure it has the right flavor and seasoning before serving it, functional verification tests a circuit to confirm it works correctly before it goes into production.

Methods of Functional Verification

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Functional verification is typically performed using the following methods:

- Simulation: Running a simulation of the design using input vectors to check the output of the circuit.

- RTL Simulation: Verifying the Register Transfer Level (RTL) description of the design using testbenches.

- Gate-Level Simulation: Simulating the synthesized gate-level netlist to verify functionality after synthesis.

- Post-Layout Simulation: Verifying the circuit after layout and routing to ensure functionality after physical design.

Detailed Explanation

There are several methods used for functional verification, and each serves a specific purpose. Simulation involves testing the design by applying various inputs (or vectors) and observing the outputs. The key types of simulations are:

1. RTL Simulation: This verifies the high-level description of the circuit using input tests, crucial during the early design phase.

2. Gate-Level Simulation: This checks the functionality after the design has been synthesized into a netlist, ensuring everything works at a physical gate level.

3. Post-Layout Simulation: After the design is completely laid out, this step ensures that the final physical arrangement still functions as intended. Each method builds upon the last, increasing confidence in the circuit's reliability.

Examples & Analogies

Imagine you are building a Lego structure. First, you might check the instruction manual (RTL simulation) to ensure each piece fits together. Once you've assembled it (gate-level simulation), you would then place it in its intended location to see if it stands up (post-layout simulation). Each stage helps you confirm the structure’s integrity and functionality.

Verification Methods for Functional Verification

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

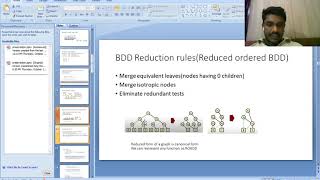

- Formal Verification: This method uses mathematical proofs to verify that the design satisfies its specifications. Formal methods involve checking that the design's behavior, as specified by the HDL code, is logically correct and consistent.

- Model Checking: Automatically verifying that a design satisfies certain properties (e.g., safety or liveness properties) by exhaustively checking all possible states.

- Equivalence Checking: Ensuring that the RTL design and its corresponding gate-level implementation are functionally equivalent.

- Property Checking: Verifying that specific properties (e.g., functional behavior, safety conditions) hold true throughout the design.

- Testbenches: Testbenches are used in simulation to apply input stimuli to the design and observe the resulting outputs. A testbench can be written in Verilog or VHDL and is used to verify functional correctness under different conditions. Functional verification involves applying a wide range of test cases to cover all possible corner cases and functional conditions.

- Random Simulation: This method involves generating random input vectors to check the design's behavior over a wide range of scenarios. Random simulation helps identify edge cases and unexpected behavior that may not be detected through traditional testbenches.

Detailed Explanation

There are several formal and informal approaches to functional verification.

1. Formal Verification explores the use of mathematical techniques to guarantee that specifications are met. Methods such as model checking examine all potential states of a design, ensuring that it adheres to properties like safety. The equivalence checking ensures consistency and correctness between different design phases.

2. Testbenches are a practical way to validate a design by applying preset inputs and checking the output, acting like a rigorous testing script. They can cover many scenarios to ensure the design is robust.

3. Random Simulation introduces unpredictability by using random inputs, uncovering edge cases that may not appear in structured testing. This method is essential for identifying unexpected behaviors in the design.

Examples & Analogies

Consider a teacher grading a test. Formal verification is like using a standard grading rubric for consistency, ensuring every answer meets specific educational standards. Testbenches resemble practice quizzes that students take to prepare for the exam, while random simulation is akin to giving the class surprise tests that gauge their true understanding of the material across unpredictable topics.

Verification Algorithms for Functional Verification

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Equivalence Checking Algorithms: These algorithms ensure that the logic of the design is preserved after transformations like synthesis, optimization, or technology mapping. The most common algorithm used is the Burch and Dill algorithm, which checks whether two designs are equivalent by comparing their state space.

- Simulation-Based Algorithms: These algorithms rely on running simulations with different sets of input vectors to check if the design behaves as expected. Coverage metrics are used to determine the effectiveness of the verification process.

Detailed Explanation

Verification algorithms play an important role in functional verification by streamlining the validation process.

1. Equivalence Checking Algorithms confirm that the design's logic remains intact even after modifications, such as synthesizing from RTL to gate-level. The Burch and Dill algorithm is a noted method for performing this check, ensuring the output remains consistent relative to the input.

2. Simulation-Based Algorithms are more practical, providing feedback on how a design operates with various inputs. They measure how well the testing covers different scenarios, leading to a more comprehensive assessment of reliability and performance.

Examples & Analogies

Think of equivalence checking as an assurance that two recipes, perhaps for the same dish, yield identical flavors after scaling the ingredients. Simulation-based assessments are like taste-testing different variations of a dish to see how it performs with various combinations of spices or cooking methods, ensuring the best overall result.

Key Concepts

-

Simulation: The method of testing a design's behavior under varying inputs.

-

Formal Verification: Validating designs mathematically for correctness.

-

Testbench: A controlled environment to apply input signals and observe outputs.

-

Random Simulation: A technique that generates random inputs to expose edge cases.

Examples & Applications

In RTL simulation, a design for an ALU is tested to ensure each arithmetic operation behaves correctly.

Formal verification confirms an industrial robot's control system adheres to safety specifications.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In VLSI we verify, each circuit's aim to satisfy.

Stories

Imagine builders constructing a bridge. Before it's used, they run tests to ensure it holds under many weights, similar to how we test circuits in functional verification.

Memory Tools

FIVE: Functional, Input, Verify, Environment — keys to test circuit functionality.

Acronyms

SFT

Simulation

Formal

Testbench — remember the main methods!

Flash Cards

Glossary

- Functional Verification

The process of ensuring that a design meets its intended functionality.

- Simulation

A method that executes the design using input vectors to verify output behavior.

- Formal Verification

A verification approach utilizing mathematical proofs to ensure a design's logical correctness.

- Testbench

A virtual environment used to test the behavior of a design through input stimuli.

- Random Simulation

Verification using randomly generated input vectors to explore various response scenarios.

Reference links

Supplementary resources to enhance your learning experience.