Verification Methods for Functional Verification

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Verification Methods

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we’ll explore the verification methods used in functional verification of VLSI designs. Can anyone tell me what functional verification means?

Is it about checking if the design works as expected according to its specifications?

Exactly! Functional verification checks that the design behaves correctly. Let’s begin with the first method: **Simulation**. What can you tell me about it?

It sounds like running tests on the design to see if it produces the right outputs!

Right! Simulation can occur at various levels - can anyone name them?

There’s RTL simulation, gate-level simulation, and post-layout simulation!

Great job! Remember the acronym RGP — RTL, Gate-level, Post-layout! Let's keep this in mind as we move ahead.

Formal Verification Techniques

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next up, let’s discuss **Formal Verification**. Can someone explain what this involves?

It uses mathematical proofs to ensure the design meets specifications?

Correct! It includes techniques like model checking. Who remembers what model checking does?

It checks design properties by going through all possible design states!

Excellent! Remember the phrase ‘All States Invoked’ to recall model checking. Now, what about equivalence checking?

That ensures the RTL and gate-level implementations are equivalent?

Exactly right! These techniques ensure the correctness of our designs throughout the verification process.

Testbenches and Random Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s discuss **Testbenches**. How do testbenches contribute to functional verification?

They apply input stimuli and check the outputs against expected results!

Exactly! Testbenches are written in languages like Verilog or VHDL and help verify functional correctness. Now, what about **Random Simulation**? How is that different?

It uses random input vectors, right? So, it can find edge cases we might miss otherwise.

Yes! Random simulation broadens our tests. Can anyone think why this might be important?

To find unexpected behaviors and improve the reliability of the design!

Exactly! Understanding both testbenches and random simulation gives us a more comprehensive view of our design.

Recap and Importance of Functional Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In summary, we focused on various methods of functional verification today. Who can list the main methods we covered?

Simulation, formal verification, testbenches, and random simulation!

Correct! Can someone briefly explain why functional verification is crucial?

Functional verification ensures designs work as intended, helping avoid errors and costly fixes later.

Exactly! It’s all about reliability in our designs. Remember this as preparation for future work in VLSI design.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Functional verification is essential in VLSI design to ensure that the design behaves as specified. This section outlines various verification methods such as simulation (RTL, gate-level, and post-layout), formal verification techniques (model checking, equivalence checking, and property checking), testbenches for applying stimuli, and the usefulness of random simulation in identifying edge cases.

Detailed

Verification Methods for Functional Verification

Functional verification is a vital process in VLSI design that ensures designs operate correctly according to specifications. The following methods are commonly employed:

1. Simulation

Simulation allows designers to run tests and check outputs against expected behavior. It can occur at multiple levels:

- RTL Simulation: Verifying the Register Transfer Level (RTL) representations using testbenches to ensure correct behavior.

- Gate-Level Simulation: Validating functionality post-synthesis by simulating the synthesized gate-level netlist.

- Post-Layout Simulation: Checking the final layout and routing of a design to ensure it still functions properly after physical design is complete.

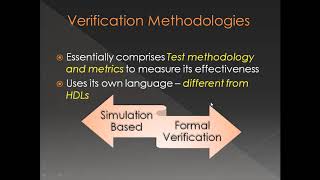

2. Formal Verification

This method mathematically proves the correctness of designs:

- Model Checking: This technique automatically verifies if design properties, like safety and liveness, hold by examining all possible states.

- Equivalence Checking: This process validates that both RTL and gate-level implementations are functionally identical.

- Property Checking: This ensures specific characteristics or behaviors are consistently true within the design.

3. Testbenches

Testbenches facilitate simulation by applying various inputs to the design, assessed for their outputs. Written in Verilog or VHDL, they are essential to testing a broad range of scenarios effectively.

4. Random Simulation

This involves generating diverse random input vectors, which helps unearth edge cases and unforeseen behaviors that traditional testbenches might miss. By testing across various scenarios, it broadens the understanding of the design’s reliability.

In conclusion, these verification methods are foundational in ensuring that VLSI designs operate as intended, thus reducing the chances of errors and promoting a robust design cycle.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Formal Verification

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Formal Verification: This method uses mathematical proofs to verify that the design satisfies its specifications. Formal methods involve checking that the design's behavior, as specified by the HDL code, is logically correct and consistent. Formal verification techniques include:

Detailed Explanation

Formal Verification is a critical method in verifying the correctness of designs in VLSI. It uses mathematical proofs to confirm that the design aligns with its specifications. This involves checking the behavior of the design as defined by the Hardware Description Language (HDL) code to ensure that it is both logically correct and consistent. This method is significant because it provides a level of assurance that cannot be achieved through simulation alone since it exhaustively checks design characteristics against requirements.

Examples & Analogies

Think of formal verification like a rigorous exam for a student. Just as the exam comprehensively tests the student’s knowledge against a set of standards, formal verification tests the design’s behavior against strict mathematical standards to ensure it functions correctly.

Techniques of Formal Verification

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

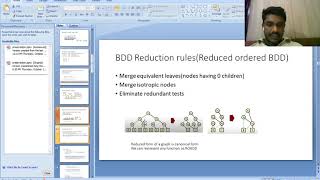

Formal verification techniques include:

- Model Checking: Automatically verifying that a design satisfies certain properties (e.g., safety or liveness properties) by exhaustively checking all possible states.

- Equivalence Checking: Ensuring that the RTL design and its corresponding gate-level implementation are functionally equivalent.

- Property Checking: Verifying that specific properties (e.g., functional behavior, safety conditions) hold true throughout the design.

Detailed Explanation

There are several specific techniques used in formal verification. Model Checking is one such technique that verifies if a design meets particular properties by exhaustively checking every possible state the design can be in. Equivalence Checking is another technique that ensures that a design remains fundamentally the same from its RTL (Register Transfer Level) representation to its gate-level representation. Property Checking focuses on verifying certain critical attributes of the design, such as its functional correctness and safety conditions, ensuring these properties are consistently maintained within the design.

Examples & Analogies

Model checking is like a detective thoroughly inspecting every room in a building to ensure no corners are left unchecked for signs of issues. Equivalence checking is similar to checking that a recipe achieves the same dish whether you follow it at a home kitchen level (RTL) or in a restaurant kitchen (gate-level). Property checking can be thought of as ensuring each time you bake a cake, it meets specific standards for taste and texture.

Testbenches

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Testbenches: Testbenches are used in simulation to apply input stimuli to the design and observe the resulting outputs. A testbench can be written in Verilog or VHDL and is used to verify functional correctness under different conditions. Functional verification involves applying a wide range of test cases to cover all possible corner cases and functional conditions.

Detailed Explanation

Testbenches are essential tools in functional verification. They act as a testing environment where various input signals can be fed into the design to observe its output. Written in programming languages like Verilog or VHDL, testbenches help verify that the design behaves correctly across numerous scenarios, including edge cases that may not be apparent under standard testing conditions. By exerting a variety of input conditions on the design, testbenches help ensure thorough functional verification.

Examples & Analogies

Consider a testbench like a pilot-run for a new airplane. Before commercial flights commence, pilots conduct various simulations to ensure the aircraft handles different weather conditions and scenarios well. Similarly, testbenches allow engineers to simulate different inputs and check if the circuit responds correctly.

Random Simulation

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Random Simulation: This method involves generating random input vectors to check the design's behavior over a wide range of scenarios. Random simulation helps identify edge cases and unexpected behavior that may not be detected through traditional testbenches.

Detailed Explanation

Random simulation adds another layer to the verification process by testing the design with inputs generated randomly. This approach aims to explore a broader spectrum of possible operational scenarios and is particularly effective at uncovering edge cases—unique situations that might not be covered by predefined input test cases. By introducing unpredictability, random simulation helps ensure that the design can gracefully handle unexpected inputs.

Examples & Analogies

Think of random simulation like throwing darts at a dartboard, where each dart represents a different input to the design. While you might have a general strategy in mind, randomizing your throws allows you to discover areas and situations that you wouldn't normally anticipate, facilitating a more thorough understanding of the design's capabilities.

Key Concepts

-

Simulation: A method to run models and validate designs against expected outputs.

-

Formal Verification: Ensuring designs are correct mathematically by proving properties.

-

RTL Simulation: A type of simulation at the Register Transfer Level to verify logic flow.

-

Testbenches: Tools that apply inputs to designs and check for the correct outputs.

-

Random Simulation: Testing a design using randomly generated inputs to find unexpected behaviors.

Examples & Applications

A testbench for a simple adder could simulate adding various pairs of numbers and checking the outputs.

Using random simulation, a designer might discover that input values producing a large output can lead to unexpected results under certain conditions.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Check the design with a simulation, make sure it meets the specification.

Stories

Once, a designer created a circuit, but it malfunctioned. They used a testbench to apply various inputs, discovering the error hidden in the random noise.

Memory Tools

Remember SIM-FOR-TES: Simulation, Formal Verification, Testbenches, and Random Simulation.

Acronyms

RIV - Remember Input Values for various checks and tests in verification.

Flash Cards

Glossary

- Simulation

The process of running a model of a design to check its outputs against expected results.

- Formal Verification

A method that uses mathematical proofs to confirm that a design meets its specifications.

- RTL (Register Transfer Level)

An abstraction used to represent a design's operation in terms of data flows between registers.

- Testbench

A collection of tests applied to a design to validate its functionality, often written in Verilog or VHDL.

- Random Simulation

A method of verifying a design by generating random input vectors to test various scenarios.

- Model Checking

A formal verification technique that examines all possible states of a design to check design properties.

- Equivalence Checking

A formal verification method that ensures two designs are functionally equivalent.

- Property Checking

The process of verifying that certain design properties are maintained across all operational conditions.

Reference links

Supplementary resources to enhance your learning experience.