Timing Verification Methods

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Static Timing Analysis (STA)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we are going to dive into Static Timing Analysis or STA. Can anyone tell me what they think STA does?

Isn't it something about checking timing without simulating the circuit?

Exactly, STA verifies if the design meets timing constraints by analyzing signal delays across all paths!

How do we know which paths to analyze?

Great question! STA takes all possible paths into account, ensuring none of them violate setup or hold times. Let's remember it as 'STA checks timing without a test'.

What happens if a path does violate timing constraints?

If a timing constraint is violated, the design needs adjustments. So, it's crucial to check with STA at multiple points in the design process.

So STA is a preventive measure?

Correct! It's there to catch potential timing issues early. Remember, it helps us ensure reliability in our designs!

Clock Tree Analysis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on to Clock Tree Analysis! Who can explain what it does?

It allows the clock signal to reach all parts of the circuit at the same time, right?

Exactly! This helps minimize clock skew, which is crucial because if the clock signals reach flip-flops at different times, it can cause incorrect operations.

Why is minimizing clock skew so important?

Minimizing clock skew ensures synchronous operation across the circuit. Let's remember it with 'Skew is clue; synchronized circuits are true!'

What techniques do we use in Clock Tree Analysis?

Common techniques involve checking the clock distribution network for delays and ensuring paths are balanced. This balance carefully manages how the signal flows.

How often should we analyze the clock tree?

Regularly throughout the design process—especially after layout changes—to ensure consistent performance.

Path-Based Timing Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's discuss Path-Based Timing Verification. Can someone tell me what a critical path is?

Isn't it the longest path in the circuit?

Correct! The critical path determines the maximum clock speed. Thus, if it doesn't meet timing requirements, the whole design fails!

How do we identify these paths?

We use algorithms specifically designed to trace the longest paths. This analysis helps focus optimization efforts where they matter most.

Can you explain how we would go about fixing a timing violation on a critical path?

We can modify the design, such as retiming or adding buffers, to improve the clock speed on those paths without losing functionality. Remember, 'Fixing critical paths means speeding laps!'

What if we miss a critical path?

We may end up with a design that doesn’t work as intended. Hence, regular path analysis is key to maintaining high-performance designs!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

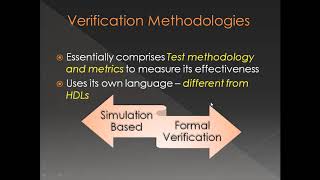

The section outlines key timing verification methods like Static Timing Analysis (STA), Clock Tree Analysis, and Path-Based Timing Verification, focusing on how these methods verify timing aspects like setup time, hold time, and clock skew in VLSI designs.

Detailed

Timing Verification Methods

In this section, we explore different timing verification methods crucial for ensuring that VLSI designs function correctly at the desired speeds without violating timing constraints. Timing verification is essential to prevent errors associated with improper timing, such as setup and hold violations, which can severely affect circuit performance.

Key Methods:

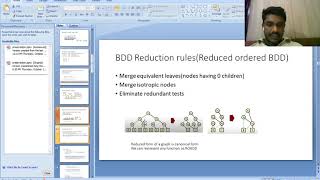

- Static Timing Analysis (STA): This method analyzes signal paths to ensure compliance with timing constraints without simulation. STA involves checking delays for all paths based on timing libraries.

- Clock Tree Analysis: This focuses on ensuring that the clock signal reaches all flip-flops simultaneously, addressing issues like clock skew, thereby enhancing performance reliability.

- Path-Based Timing Verification: It examines the timing of critical paths in the circuit to ensure performance targets are met, especially significant in high-speed designs.

Understanding these methods is vital for engineers as they provide the framework for verifying the timing correctness necessary for the reliable operation of VLSI systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Static Timing Analysis (STA)

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Static Timing Analysis (STA): STA is a method used to verify whether the timing constraints of the design are met without the need for simulation. It checks the delay of all signal paths in the design and ensures that there are no timing violations, such as setup or hold violations. STA operates by analyzing the timing of all paths in the design using the timing library and propagation delay information.

Detailed Explanation

Static Timing Analysis (STA) is a method employed in VLSI design to ensure that the circuit meets its timing requirements. Unlike simulation methods that run tests dynamically, STA evaluates all possible signal paths mathematically. It checks if there are any timing violations, such as setup or hold violations. Essentially, it calculates how long signals take to traverse the pathways within the circuit and compares those times against established thresholds. Using timing libraries that provide delay data for each component, STA ensures that every possible route through the design adheres to the specified timing constraints.

Examples & Analogies

You can think of STA like a train scheduling system in a city. Just as the system must ensure that trains leave and arrive at their scheduled times without overlap, STA verifies that signals in a circuit arrive at specific points in time, maintaining a precise schedule. If a train (or signal) arrives too early or too late, it can cause delays in the entire network.

Clock Tree Analysis

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Clock Tree Analysis: This is part of timing verification where the clock tree, which distributes the clock signal across the design, is analyzed to ensure that all flip-flops receive the clock signal at the correct time. The goal is to minimize clock skew and ensure that the clock signal arrives simultaneously at all flip-flops.

Detailed Explanation

Clock Tree Analysis focuses on the distribution of the clock signal throughout the circuit, particularly to flip-flops. The clock signal is crucial because it synchronizes operations in the design. In this analysis, engineers examine how the clock signal propagates through the clock tree—a special arrangement of wires designed to distribute the clock efficiently. A key issue that Clock Tree Analysis addresses is clock skew, which is the difference in arrival times of the clock signal to different flip-flops. By minimizing skew, designers ensure that all parts of the circuit are synchronized, preventing timing-related errors.

Examples & Analogies

Imagine a conductor leading an orchestra. If some musicians start playing before others get the signal, the music will sound out of sync. Similarly, if flip-flops in a circuit don't receive the clock signal simultaneously, it can cause timing issues. Clock Tree Analysis ensures that every 'musician' (flip-flop) begins playing at precisely the right moment so that the entire circuit operates harmoniously.

Path-Based Timing Verification

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Path-Based Timing Verification: In path-based verification, the delay of critical paths is checked to ensure that they meet timing requirements. This is particularly important for high-speed designs where the timing of specific paths can determine the performance of the entire circuit.

Detailed Explanation

Path-Based Timing Verification is a focused approach that examines the timing of specific critical paths within the circuit design. A critical path is the longest necessary route that signals must traverse from input to output, determining the overall performance and maximum speed of the circuit. By analyzing these paths to ensure they meet required timing constraints, designers can identify potential bottlenecks and optimize the design for improved performance. This kind of verification is especially crucial in high-speed designs, where even the slightest delays can lead to errors.

Examples & Analogies

Think of a busy highway where the flow of traffic depends on the longest red light. If one intersection has a longer light duration than the rest, it can cause a traffic jam, slowing down the entire route. Path-Based Timing Verification is like making sure that the traffic lights are synchronized so that the longest waiting time doesn’t hold up the rest of the traffic, ensuring smooth and fast movement through the circuit.

Key Concepts

-

Static Timing Analysis: A method for checking timing constraints in designed circuits without simulations.

-

Clock Tree Analysis: Ensures clock signals arrive at flip-flops simultaneously, minimizing clock skew.

-

Critical Path: The longest path in a circuit affecting the maximum operational speed.

Examples & Applications

If a flip-flop has a setup time of 10ns and a hold time of 5ns, the design must ensure that the signal arriving at the flip-flop maintains these stable periods.

During clock tree analysis, an unexpected clock skew of 2ns can cause timing violations if one flip-flop triggers before another.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To keep clock signals aligned and neat, secure the path for timing's complete.

Stories

Imagine a relay race where runners start at different times—this is what happens if clocks are skewed in a circuit. Ensuring all runners start at the same time is crucial for a fair race, much like minimizing clock skew ensures reliability in circuits.

Memory Tools

S.C.C. for timing analysis: S - Static timing, C - Clock tree, and C - Critical paths!

Acronyms

STA for Static Timing Analysis, which tells us about path timings!

Flash Cards

Glossary

- Static Timing Analysis (STA)

A method of verifying timing constraints in digital circuits without requiring simulation.

- Clock Tree Analysis

The process of analyzing the clock distribution network to ensure synchronized arrival of clock signals to all flip-flops.

- Critical Path

The longest delay path through a circuit, determining the maximum clock speed achievable.

- Setup Time

The minimum time before the clock edge that the input of a flip-flop must be stable.

- Hold Time

The minimum time after the clock edge that the input of a flip-flop must remain stable.

Reference links

Supplementary resources to enhance your learning experience.