Hybrid Verification Approaches

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Hybrid Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we’re going to discuss hybrid verification approaches in VLSI design. With designs getting more complex, it's crucial to ensure that both functionality and timing are validated. Can anyone tell me what we mean by 'hybrid' in this context?

Is it when we combine multiple methods for verification?

Exactly right, Student_1! We combine methods like functional verification with timing analysis. What methods do you think we might be combining?

Maybe simulation with some sort of timing analysis?

Exactly, great thinking! We often use Simulation + Static Timing Analysis or combine Formal + Simulation methods for better results. Let’s dive deeper into why these combinations are important.

Simulation and STA

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start with the first approach: Simulation combined with Static Timing Analysis. Why do you think it’s beneficial to use both?

It sounds like you can check both behavior and timing at the same time.

Precisely! By using simulation, we can see how the circuit behaves under different inputs, while STA ensures that we’re within timing constraints. Can someone give me examples of timing constraints that we should check?

Setup and hold times, right?

That’s correct! It’s all about ensuring that our design meets these critical timing constraints.

Formal Verification and Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s talk about combining Formal Verification with Simulation. What do you think are the advantages of this combination?

Maybe we can cover more corner cases that are hard to simulate?

Absolutely, Student_1! Formal verification helps us mathematically prove certain properties hold true, while simulation allows us to see real-world behavior. Why is that important for VLSI designs?

Because it helps catch errors early on that might be missed otherwise?

Exactly! Catching those errors early saves time and resources in the long run. It’s crucial for the overall success of the VLSI design.

Challenges in Hybrid Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

While hybrid approaches are powerful, what challenges do you think designers might face when implementing them?

Maybe the complexity of the designs makes it tough to verify everything thoroughly?

Exactly! Larger designs lead to an expanded state space, making verification tedious. Additionally, the cost of computation becomes significant. What strategies can mitigate these challenges?

Using automated tools or focusing on critical paths?

Good strategies! Prioritizing critical areas helps optimize time and resources during the verification process.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

As VLSI designs grow ever more complex, hybrid verification approaches that integrate functional and timing verification techniques have gained prominence. These approaches leverage simulation and formal methods to ensure both correctness and performance, aiding designers in early detection of timing violations and edge cases.

Detailed

Hybrid Verification Approaches

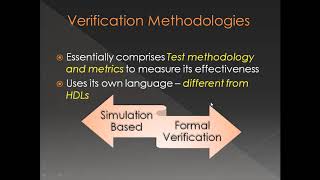

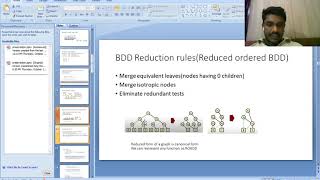

As designs in Very-Large-Scale Integration (VLSI) technology become increasingly complex, hybrid verification approaches have emerged as a vital strategy for ensuring both functional integrity and adherence to timing constraints. The key techniques in hybrid verification typically involve combining Simulation with Static Timing Analysis (STA) and integrating Formal Verification with Simulation.

Key Approaches:

- Simulation + STA: This approach allows designers to verify the correct operational behavior of the circuit while simultaneously ensuring that all timing requirements are satisfied. Early detection of timing violations is crucial to streamlining the design process and mitigating potential issues down the line.

- Formal + Simulation: Combining formal verification methods with simulation enhances the ability to prove the functionality and performance of a design. This method helps cover edge cases that might not be easily captured or tested using simulation alone. By utilizing rigorous mathematical proofs alongside practical simulations, designers can produce more reliable VLSI designs.

The significance of hybrid verification lies in its ability to address the growing challenges of verification as the complexity of circuits continues to increase.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Hybrid Verification Approaches

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As designs become more complex, hybrid verification approaches combining both functional and timing verification have become increasingly common.

Detailed Explanation

This chunk introduces the concept of hybrid verification approaches in VLSI design. It highlights that as electronic designs grow in complexity, it becomes necessary to utilize strategies that incorporate both functional verification (ensuring that the design operates correctly as intended) and timing verification (ensuring that the design meets timing requirements). The integration of both verification types allows for a more comprehensive assessment of the design, addressing potential issues in both areas simultaneously.

Examples & Analogies

Think of hybrid verification as a thorough check-up at a doctor. Just as a doctor evaluates not just symptoms but also conducts tests to check overall physical health, hybrid verification examines the functionality and timing aspects of a design to ensure it works properly and efficiently.

Simulation + STA

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Simulation + STA: By combining simulation and static timing analysis, designers can verify that the design behaves correctly under functional conditions while also meeting timing constraints. This approach helps ensure that timing violations are detected early in the design process.

Detailed Explanation

In this chunk, the focus is on one of the hybrid approaches: combining simulation with static timing analysis (STA). Simulation allows designers to observe how the circuit performs under various input conditions, establishing that the design works as intended. At the same time, STA evaluates whether the design meets timing requirements without performing actual simulations. By using both methods together, designers can catch potential timing issues early, which can save significant trouble later in the design process.

Examples & Analogies

Imagine you're preparing for an important presentation. You would likely practice in front of a mirror (simulation) to ensure your delivery is smooth and engaging. Meanwhile, you might check your timing to ensure you stay within the allotted time limit (STA). Doing both allows you to deliver a well-executed presentation without running over time.

Formal + Simulation

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Formal + Simulation: Formal verification techniques are combined with simulation-based methods to prove the correctness of the design's functionality while covering edge cases not easily captured through simulation alone.

Detailed Explanation

This chunk explains another hybrid approach that integrates formal verification and simulation. Formal verification employs mathematical methods to rigorously prove that certain properties of the design hold true, ensuring logic consistency. On the other hand, simulation allows for more practical testing of design scenarios, including edge cases. By combining these two approaches, designers can ensure that their design is both theoretically sound and practically validated, addressing potential gaps that only one method may cover.

Examples & Analogies

Consider it like preparing for a competitive examination. You might study theoretical concepts (formal verification) to understand the foundational principles while also taking practice tests (simulation) to get familiar with the exam format and types of questions. This way, you ensure not only do you know the material but also are prepared for how it will be presented.

Key Concepts

-

Hybrid Verification: A strategy combining various methods to ensure both functional and timing correctness.

-

Simulation + STA: A combined approach that enhances verification by checking behavior and timing simultaneously.

-

Formal + Simulation: A method that marries formal proofs with practical simulations to cover edge cases.

Examples & Applications

An example of a simulation combined with STA could involve checking a flip-flop circuit to ensure it operates within its required timing specifications while also verifying that it switches states correctly under different input conditions.

A design might use formal verification methods to mathematically prove a property about state transitions while also conducting simulations to observe how the design reacts to unexpected inputs.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To verify and confirm; with timing and function to learn.

Stories

Once, in a land of circuits and chips, a wise designer used both simulation and formal methods to avoid pitfalls, ensuring her designs passed the toughest tests of timing.

Memory Tools

HFS: Hybrid, Formal, Simulation.

Acronyms

STA

Static Timing Analysis.

Flash Cards

Glossary

- Hybrid Verification

Combining different verification methods, such as functional and timing verification, to ensure a comprehensive assessment of VLSI designs.

- Static Timing Analysis (STA)

A method that verifies timing constraints without simulation by analyzing signal path delays.

- Formal Verification

A mathematical approach to verifying that a design meets specified properties and behaves correctly.

- Design Complexity

The increasing intricate interconnections and functionalities of VLSI systems which make verification challenging.

Reference links

Supplementary resources to enhance your learning experience.