Conclusion

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of Verification in VLSI Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we are going to delve into the importance of verification in VLSI design. Can anyone explain why verification is necessary?

I think it’s to make sure the design works as it's supposed to.

Correct! Verification helps us confirm that circuits behave as intended. It’s essential to avoid costly errors in the design phase. Remember: 'Find it early, fix it cheap!'

What happens if there's a mistake in the design?

Great question! Mistakes can lead to malfunctioning devices, which can be costly to fix after production. Let’s summarize: verification is necessary to ensure functionality and avoid expensive errors later.

Functional and Timing Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s discuss the two main types of verification: functional and timing. Who can tell me the difference?

Functional verification checks if the design works right, and timing verification checks if it works fast enough?

Exactly! Functional verification ensures the design meets specifications under various conditions, while timing verification focuses on meeting speed requirements without violations.

So both are important for overall performance?

Absolutely! They complement each other to ensure that the VLSI design performs correctly and efficiently. Remember this: Functional = correctness; Timing = speed.

Advancements in Verification Methods

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

As VLSI technology evolves, verification methods must also adapt. Why do you think this evolution is necessary?

Because designs are getting more complex?

Yes! With increasing design complexity, we need sophisticated algorithms to ensure accuracy. What verification methods can you recall from our previous lessons?

Simulation, static timing analysis, and formal verification techniques?

Correct! These methods ensure we keep pace with evolving design challenges. In summary, the verification landscape is not static but rather dynamic, necessitating continuous improvements.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In the conclusion of this chapter, the importance of verification in ensuring that VLSI designs function according to specifications and meet timing requirements is underscored. Verification algorithms play a pivotal role in validating these designs, and as technology advances, so too must the techniques used for verification.

Detailed

Conclusion

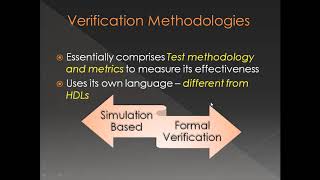

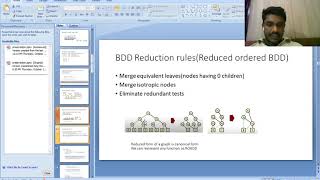

Verification is a crucial phase in the VLSI design process, confirming that each circuit operates as intended and aligns with specified timing requirements. Functional verification ensures that designs behave correctly under a variety of test conditions, whereas timing verification guarantees operations at the required clock speeds. Various verification algorithms, such as simulation-based methods, formal verification, and static timing analysis, are vital for validating increasingly complex VLSI circuits. As advancements in VLSI technology continue, the methods of verification must evolve to address these growing complexities effectively.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Verification in VLSI Design

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Verification is an essential step in the VLSI design flow, ensuring that the circuit functions as expected and meets timing constraints.

Detailed Explanation

Verification in VLSI design is crucial because it checks whether the circuit behaves as intended and satisfies both functional and timing specifications. It acts as a safeguard against errors that could occur during the design process, ensuring that the final product performs accurately and efficiently within the predetermined limits.

Examples & Analogies

Think of verification like a quality check in a factory. Just as a factory checks products to ensure they meet safety and quality standards before shipping them out, VLSI verification ensures that circuits function correctly and are ready for deployment.

Functional vs. Timing Verification

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Functional verification guarantees that the design operates correctly under various conditions, while timing verification ensures that the design can operate at the desired clock speed without timing violations.

Detailed Explanation

Functional verification focuses on checking that all features of the circuit work as per specifications. It tests the logic and behavior of the design during different operational states. Timing verification, on the other hand, inspects whether the design meets specific timing requirements, like operating at a certain speed without encountering delays that could impact its performance or cause failures.

Examples & Analogies

Imagine you’re training for a marathon. Functional verification is like making sure you can run the distance without stopping, while timing verification is ensuring you do it within a certain time to meet your goals.

Role of Verification Algorithms

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Verification algorithms, including simulation-based methods, formal methods, and static timing analysis, are crucial for validating large and complex VLSI designs.

Detailed Explanation

Verification algorithms are sophisticated techniques used in the VLSI design process to ensure that the circuit meets all required specifications. Simulation-based methods test the design by simulating different input scenarios to observe outputs. Formal methods provide a mathematical framework to prove correctness, while static timing analysis checks the timing constraints without relying on simulation.

Examples & Analogies

It's like using different tools for a home repair project. Just as you’d use a tape measure to check lengths (static timing analysis), a level to ensure everything is straight (simulation), and structural analysis to ensure safety (formal methods), each verification algorithm helps ensure that the VLSI design is thorough and accurate.

Evolving Verification Techniques

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

As VLSI technology continues to evolve, verification techniques must continue to adapt to meet the increasing complexity of modern designs.

Detailed Explanation

With advancements in technology, VLSI designs are becoming more complex, necessitating more sophisticated verification methods. The verification process must evolve to address challenges such as large design sizes and intricate timing analysis, ensuring that reliability and correctness are maintained as circuit specifications become more demanding.

Examples & Analogies

Just as software updates are necessary to improve app functionality and security, verification techniques need continual updates to effectively tackle the growing complexity of VLSI designs and ensure accuracy in performance.

Key Concepts

-

Verification: Ensures VLSI designs work as intended and meet specifications.

-

Functional Verification: Validates functionality under various conditions.

-

Timing Verification: Confirms operation at required clock speeds without violations.

-

Verification Algorithms: Key techniques for validating complex designs.

Examples & Applications

Using simulation tools to check the functionality of a processor design.

Applying static timing analysis to ensure the design can operate at a frequency of 1GHz without timing violations.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In VLSI, verification's the key, to make sure circuits work, you see.

Stories

Imagine crafting a new car; before it hits the road, you test every part to ensure it rolls smoothly, much like verifying a VLSI design for correct functionality and timing.

Memory Tools

FVT stands for Functional Verification and Timing Verification.

Acronyms

VVS

Verify

Validate

Succeed in ensuring efficient VLSI designs.

Flash Cards

Glossary

- Functional Verification

Validation that a design behaves correctly according to specifications.

- Timing Verification

Ensures that a design meets required timing constraints for proper operation.

- Static Timing Analysis (STA)

A method to verify timing constraints without simulation, analyzing delays in signal paths.

- Simulation

Running a representation of the design to validate its performance under specified conditions.

- Formal Verification

Using mathematical methods to prove the correctness of designs against specifications.

- Verification Algorithms

Techniques used to ensure a design meets both functional and timing specifications.

Reference links

Supplementary resources to enhance your learning experience.