Simulation

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll talk about simulation and why it's crucial in FPGA design. Who can tell me what happens if we skip this step?

I think we could end up with a circuit that doesn't work correctly.

Exactly! Skipping simulation can lead to undetected errors. Simulation allows us to verify functionality before implementation. Does anyone know what types of errors we might discover?

Logic errors and timing violations?

Correct! Just remember 'L.E.T' for Logic errors, Timing violations. Let's move to how we write a testbench to simulate our design.

Creating a Testbench

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

A testbench is vital for simulation. It's a separate module. Can anyone explain the purpose of a testbench?

To apply test inputs and check outputs without affecting the actual design?

Exactly! Now, let's look at how we write a testbench for a 4-bit binary adder. What inputs do you think we should test first?

Different combinations of A and B, plus the carry input?

Right! In our testbench, we will provide various combinations to fully test the adder. Remember, we check outputs against expected values.

Analyzing Outputs

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Once we've applied our inputs, we need to analyze the outputs. How does this help us?

It shows whether our design is working as intended or if we need to fix something.

Exactly! If the outputs match our expectations, we verify the functionality. If not, we have to debug our design. What do you think will happen next?

We would have to revise our VHDL or Verilog code?

Correct! Debugging is a critical part of the design flow. Always remember - 'Check before you build!'

Final Thoughts on Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up today's session, let’s summarize why simulation is vital in FPGA design.

It helps detect errors early and ensures the design works correctly.

Exactly! Simulation can save time and resources in the long run. Remember, 'Simulate before you implement!' Can anyone recall the three main types of issues we may face if we skip simulation?

Logic errors, timing violations, and race conditions!

Fantastic! Great job today, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the importance of simulation in the FPGA design flow. It includes writing testbenches for VHDL and Verilog, ensuring that the design functions as intended and identifying errors early in the development process.

Detailed

Simulation

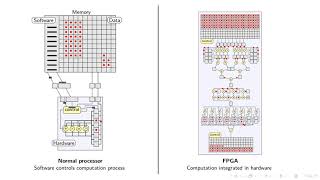

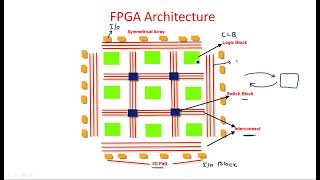

Simulation is essential for ensuring that a digital circuit behaves according to its specifications before it is implemented on an FPGA. This section emphasizes that effective simulation helps detect logic errors, race conditions, and timing violations early in the design flow, which can save significant time and resources.

Writing a Testbench for Verification

A testbench is a dedicated module in VHDL or Verilog used to apply input stimuli and monitor the outputs of your design. It serves as a testing environment that does not affect the actual design. By simulating the design using a testbench, designers can validate their designs and ensure they meet the predefined specifications.

Examples of Testbenches

For both VHDL and Verilog, examples highlight how to create testbenches for a simple 4-bit binary adder. The examples provide a structured approach to applying inputs over time and checking the outputs against expected results. The VHDL testbench demonstrates the use of signals and component instantiation, while the Verilog example shows a direct implementation of the adder module with initial conditions.

Importance of simulation cannot be overstated, as it significantly enhances the reliability of digital designs by allowing for rigorous testing under various conditions before the final hardware realization.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Simulation

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Before implementing the design on the FPGA, it is important to verify the functionality of the digital circuit using simulation. Simulating the design helps detect logic errors, race conditions, or timing violations early in the process.

Detailed Explanation

Simulation is a critical step in the design process of digital circuits. It allows designers to test their designs in a virtual environment before they are physically implemented on an FPGA. By simulating the circuit, any potential issues, such as logic errors (mistakes in the function of the circuit), race conditions (situations where the timing of events can lead to unpredictable results), or timing violations (when signals do not meet the required timing specifications) can be discovered early. This way, designers can save time and resources by resolving issues before the design is fabricated.

Examples & Analogies

Imagine building a prototype of a car before it goes into full production. You would want to test the car in various conditions to ensure everything works as intended—checking the brakes, steering, and engine performance. Similarly, simulation acts like a virtual test drive of your digital circuit, allowing designers to catch and fix any problems before the circuit is put into actual use.

Testbench Overview

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A testbench is a VHDL or Verilog module that generates input stimuli and checks the outputs of the design.

Detailed Explanation

A testbench serves as the testing environment for your design. It is structured as a separate module that does not become part of the final circuit. Instead, the testbench generates different input signals, or 'stimuli', that the original design will respond to, and it also monitors the output responses. This allows the designer to verify if the outputs meet the expected results based on the inputs given.

Examples & Analogies

Think of a testbench like a teacher conducting a quiz. The teacher (testbench) prepares various questions (input signals) for the students (the circuit), and then checks the answers (outputs) to ensure they are correct. If a student answers incorrectly, the teacher can provide immediate feedback to help them learn.

Writing a Testbench for the 4-Bit Adder

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Here's an example of a simple testbench for the 4-bit adder:

VHDL Testbench:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY TB_ADDER_4BIT IS

END ENTITY TB_ADDER_4BIT;

ARCHITECTURE behavior OF TB_ADDER_4BIT IS

SIGNAL A, B : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL Cin : STD_LOGIC;

SIGNAL Sum : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL Cout : STD_LOGIC;

COMPONENT ADDER_4BIT

PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Cin : IN STD_LOGIC;

Sum : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

Cout : OUT STD_LOGIC);

END COMPONENT;

BEGIN

uut: ADDER_4BIT PORT MAP (A => A, B => B, Cin => Cin, Sum => Sum, Cout => Cout);

stim_proc: PROCESS

BEGIN

A <= "0001"; B <= "0010"; Cin <= '0'; WAIT FOR 10 ns;

A <= "1111"; B <= "0001"; Cin <= '1'; WAIT FOR 10 ns;

A <= "0101"; B <= "1010"; Cin <= '0'; WAIT FOR 10 ns;

WAIT;

END PROCESS;

END ARCHITECTURE behavior;

Detailed Explanation

In the provided VHDL testbench code for the 4-bit adder, several key components are outlined. The testbench includes a declaration for input and output signals specific to the adder. It also contains the 'uut' (Unit Under Test) instantiation, which connects the adder to the testbench. The 'stim_proc' process is where the input test cases are defined: it sets specific values for inputs A, B, and Cin and waits a short duration before changing them. By simulating these inputs, designers can observe if the adder produces the correct output Sum and Cout.

Examples & Analogies

Consider this testbench as a teacher assigning homework problems to students to ensure they understand the material. The teacher gives specific problems (input vectors) and checks the students’ answers (outputs) to see if they’ve understood the concepts. Just as the teacher anticipates the correct answers, the testbench expects specific outputs for given inputs to validate the design.

Verilog Testbench

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Verilog Testbench:

module TB_ADDER_4BIT;

reg [3:0] A, B;

reg Cin;

wire [3:0] Sum;

wire Cout;

ADDER_4BIT uut (A, B, Cin, Sum, Cout);

initial begin

A = 4'b0001; B = 4'b0010; Cin = 0; #10;

A = 4'b1111; B = 4'b0001; Cin = 1; #10;

A = 4'b0101; B = 4'b1010; Cin = 0; #10;

$finish;

end

endmodule

Detailed Explanation

Similar to the VHDL testbench, this Verilog testbench for the 4-bit adder is structured to simulate the same operations. The module declares input and output signals and instantiates the adder. The 'initial' block is crucial as it sets the initial conditions for A, B, and Cin and specifies the sequence of inputs while introducing a time delay between them. This enables the observes of the outputs after each set of inputs, validating that the design behaves as expected.

Examples & Analogies

If we compare this to a cooking scenario, the testbench behaves like a chef who follows a recipe step by step, adding specific ingredients (inputs) and mixing them together at designated times (waiting). After mixing, the chef checks if the dish (output) is cooked perfectly, ensuring everything is done in the right sequence and timing.

Key Concepts

-

Simulation: The process of verifying design functionality before hardware implementation.

-

Testbench: A specific module for generating inputs and analyzing outputs.

-

Logic Error: Errors in the logic of the design that prevent correct operation without showing a failure.

-

Timing Violation: A situation where a signal does not meet timing requirements, causing malfunctions.

-

Race Condition: Conditions that depend on the timing of events, leading to unpredictable circuit states.

Examples & Applications

For both VHDL and Verilog, examples highlight how to create testbenches for a simple 4-bit binary adder. The examples provide a structured approach to applying inputs over time and checking the outputs against expected results. The VHDL testbench demonstrates the use of signals and component instantiation, while the Verilog example shows a direct implementation of the adder module with initial conditions.

Importance of simulation cannot be overstated, as it significantly enhances the reliability of digital designs by allowing for rigorous testing under various conditions before the final hardware realization.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Before we make, we must simulate, so our circuits won't suffer fate.

Stories

Once, a designer skipped simulation; their circuit failed during demonstration. A lesson learned, they vowed to test, ensuring all designs would pass the quest.

Memory Tools

Remember 'S.L.T.R.' during simulation: 'Simulate, Log, Test, Revise.'

Acronyms

SPECT

Simulation

Potential errors

Evaluate

Check

Test.

Flash Cards

Glossary

- Simulation

A process of testing and verifying a design by running it with a testbench to check the behavior and outputs.

- Testbench

A module that generates input stimuli and checks outputs of the design without affecting the actual functionality.

- Logic Error

An error in the design that causes incorrect functionality but does not necessarily cause the design to fail.

- Timing Violation

A scenario where a signal does not arrive at its destination within the required time constraints.

- Race Condition

A situation where the system's behavior is dependent on the timing of events, leading to unpredictable results.

Reference links

Supplementary resources to enhance your learning experience.