Synthesis

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're diving into an essential part of the FPGA design process known as synthesis. Can anyone tell me what happens during this stage?

Isn't it where we convert the code into something the FPGA can understand?

Exactly, we take our HDL code and transform it into a netlist. This is a key step because it allows us to map our design to physical hardware. Does anyone remember what HDL stands for?

Hardware Description Language!

Correct! Now, synthesis helps ensure our design is optimized. Can anyone think of a reason why optimization might be important?

To make sure it runs efficiently?

Yes! We aim for improved performance and reduced resource usage. So remember, synthesis begins the journey of converting our creative designs into practical implementations!

Details of the Synthesis Process

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand what synthesis is, let’s look at how this process unfolds. Anyone want to share what they think happens step by step?

You write the HDL code, then what? Does it just magically become a netlist?

I wish it were that simple! After writing the HDL, synthesis tools analyze the code, creating a netlist representation first. Can you guess what the next crucial step might be?

Optimization? So it checks for performance issues?

Right! Synthesis tools apply various optimization techniques to improve the design. Lastly, they check for errors, providing warnings if something doesn’t look quite right.

So synthesis is both about creating the netlist and ensuring everything will work as expected?

Absolutely! This is why synthesis is crucial in our design flow.

Significance of Synthesis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s reflect on the significance of synthesis. Why do you believe it’s so pivotal in the FPGA design flow?

It sets us up to be ready for the next stages, right?

Exactly! Without proper synthesis, we could face serious issues during the implementation phase. What could happen if we skip synthesis or don't optimize?

I guess the design might not fit the FPGA properly, or it could run too slow.

Correct! That's why we must take synthesis seriously to ensure we maximize the potential of our FPGA designs.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The synthesis stage transforms the hardware description language (HDL) code into a netlist representation of logical gates and components that the FPGA will utilize. It's instrumental in ensuring that designs are optimized for real-world implementation, significantly impacting overall performance.

Detailed

Synthesis

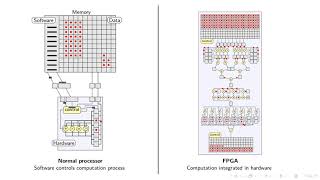

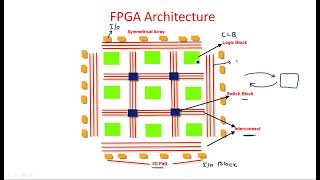

In the FPGA design flow, synthesis represents a critical stage where the hardware description language (HDL) codes written in VHDL or Verilog are converted into a netlist. This netlist contains the logical representation of the circuit comprising logical gates and other components necessary for the FPGA implementation. During synthesis, optimization techniques are applied to ensure that the design meets constraints such as timing and resource usage efficiently.

Key Points:

- Conversion of HDL to Netlist: The primary function of synthesis is to convert the written HDL code into a netlist that embodies the design in terms of logical gates and connections. This process involves transforming high-level constructs (like addition or logic operations) into specific hardware arrangements.

- Optimization: Synthesis tools often incorporate optimization algorithms that help refine the design for better performance, reduced power consumption, and efficient resource utilization within the FPGA.

- Error Detection: Synthesis also serves as a checkpoint to flag any potential design issues before proceeding to the implementation phase.

Overall, successful synthesis is fundamental in transforming design ideas into working digital circuits realized on FPGA devices.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

What is Synthesis?

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

○ Convert the hardware description into a netlist that represents the logical gates and components to be implemented on the FPGA.

Detailed Explanation

Synthesis is the process of transforming your written hardware description language (HDL) code (like VHDL or Verilog) into a netlist. A netlist is essentially a diagram that represents all the logical parts of your circuit—in simpler terms, it shows how the components interact with each other using logical connections. This step is crucial because it prepares your design to be physically implemented on the FPGA by defining how the logical gates will fit together.

Examples & Analogies

Think of synthesis as transforming a recipe written in a cookbook (your HDL code) into a grocery list (the netlist). The recipe provides step-by-step instructions to create a dish, while the grocery list organizes all the necessary ingredients and quantities needed to make it. Just as you can't cook without a grocery list, you can't create a circuit on an FPGA without a netlist.

Tools for Synthesis

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Synthesis Tools: Vivado (Xilinx), Quartus (Intel), or other FPGA vendor-specific tools.

Detailed Explanation

There are various synthesis tools available to help with the process of turning HDL code into a netlist. Popular examples include Vivado, developed by Xilinx, and Quartus, made by Intel. Each of these tools can understand your design's HDL code and will carry out the synthesis process, translating your high-level instructions into a format that can be used by the FPGA.

Examples & Analogies

Using a synthesis tool is like using software to convert a text document into different file formats. For instance, you might write a

Key Concepts

-

Synthesis: A step in the FPGA design flow where HDL code is transformed into a netlist.

-

Netlist: A representation of the digital circuit composed of logic gates and connections.

-

Optimization: Techniques applied during synthesis to enhance performance and efficiency.

Examples & Applications

Converting a 4-bit adder HDL code into a netlist that outlines how the adder functions with logical gates.

Using synthesis tools to improve timing and resource usage for a digital circuit design.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Synthesis makes it fit, turning code into circuitry bit by bit.

Stories

Imagine a chef turning a recipe's ingredients into a dish. The synthesis process is like the cooking phase, transforming raw ingredients (the HDL) into a finalized meal (the netlist).

Memory Tools

Netlist = "Gates Connected" (Just visualize the netlist as the 'net' that catches all gates together).

Acronyms

S.O.N. - Synthesis, Optimization, Netlist. Remember these key processes!

Flash Cards

Glossary

- Synthesis

The process of converting HDL code into a netlist that represents the design in terms of logical gates and components for FPGA implementation.

- Netlist

A data structure that contains a detailed description of the components and their interconnections in a digital circuit.

- HDL (Hardware Description Language)

A specialized computer language used to describe the structure and behavior of electronic circuits.

- Optimization

The process of improving the performance and resource usage of a design during synthesis.

Reference links

Supplementary resources to enhance your learning experience.