VHDL Example: 4-Bit Binary Adder

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to VHDL and Its Structure

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to dive into VHDL, which stands for VHSIC Hardware Description Language. It's vital for describing the behavior and structure of electronic systems.

What does VHSIC stand for?

Great question! VHSIC stands for Very High-Speed Integrated Circuit. Now, let’s remember this acronym: ‘VHSIC’ - Vibrant Hardware Signals Interconnecting Components.

How does this relate to our 4-bit adder?

The 4-bit adder is a great example to see VHDL in action! We’ll see how it helps specify the functionality of our circuit.

Entity and Architecture Components

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In VHDL, the main components are the entity and architecture. The entity defines the inputs and outputs, while the architecture describes how these components interact.

Can you give an example of what defines inputs and outputs?

Sure! For our 4-bit adder, we have inputs as two 4-bit vectors, A and B, and a carry-in, Cin. The outputs are the 4-bit sum and a carry-out. Remember: 'Inputs into Outputs'.

What do we need to declare in the architecture?

In the architecture, we define a process that includes the logic for the addition operation. This process is crucial for the behavior of our adder.

Addition Logic in VHDL

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s discuss the logic of addition. In our architecture, we use the '+' operator to compute the sum, while the carry-out requires some logical thinking.

How is the carry-out calculated?

The carry-out is calculated by checking the most significant bits of inputs A and B, and the carry-in. Here’s a mnemonic: ‘Check Carry: A, B, and Cin’. This helps ensure we handle all carry conditions.

So, if both A and B have their highest bit as 1, we should definitely expect a carry-out?

Exactly! This confident approach will help you solve addition in VHDL effectively.

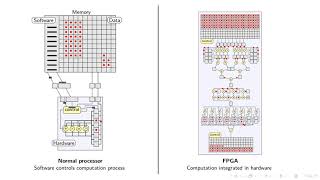

Deploying the VHDL Code for FPGA

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

After writing our VHDL code, which describes the logic of the adder, we need to simulate it to see how it performs before deploying it onto the FPGA.

How do we simulate the VHDL code?

We use testbenches, which are specific VHDL modules designed to generate stimuli for our adder. Think of it as prepping your circuit for real-world conditions.

Is it crucial to test all input scenarios?

Yes! Comprehensive testing ensures that our binary adder functions correctly under all circumstances.

Summary of VHDL Components for Binary Adder

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s summarize what we’ve learned about the 4-bit binary adder in VHDL. We began with defining entities, moved through architectures, and explored addition logic.

And how the carry-out is computed!

Plus the importance of testbenches for simulation.

Exactly! These components lay the foundation for understanding VHDL in FPGA applications.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

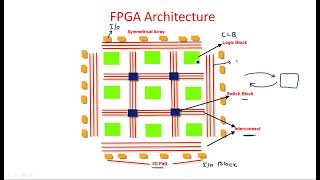

It highlights the various components of the 4-bit binary adder’s VHDL code, including port declarations and the process to compute the sum and carry-out. Understanding this serves as a practical example of translating designs into FPGA code.

Detailed

The section details how to implement a 4-bit binary adder in VHDL, starting with the library and entity definitions, followed by the architecture section which includes the main process for executing the addition logic. This example showcases the input ports for two 4-bit binary numbers and a carry-in, along with output ports for the sum and carry-out, establishing a clear illustration of how to convert high-level designs into functional VHDL code for FPGA deployment.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

VHDL Libraries and Entity Declaration

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_unsigned.ALL; ENTITY ADDER_4BIT IS PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0); B : IN STD_LOGIC_VECTOR(3 DOWNTO 0); Cin : IN STD_LOGIC; Sum : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); Cout : OUT STD_LOGIC ); END ENTITY ADDER_4BIT;

Detailed Explanation

In this chunk, we start by defining the necessary libraries that enable the use of standard logic types in VHDL. We then declare an entity named ADDER_4BIT. An entity in VHDL essentially describes the interface of our circuit, outlining its inputs and outputs. The PORT section specifies two 4-bit input signals (A and B), a carry input (Cin), and the outputs for sum (Sum) and carry-out (Cout). This setup is necessary to set the groundwork for our binary adder circuit.

Examples & Analogies

Think of an entity declaration like setting up a recipe. Just like you need to list out all the ingredients (inputs) and what you expect to serve at the end (outputs, like the final dish), the entity does the same for the digital circuit.

Architecture Definition and Process Block

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

ARCHITECTURE behavior OF ADDER_4BIT IS BEGIN PROCESS (A, B, Cin) BEGIN Sum <= A + B + Cin; Cout <= (A(3) AND B(3)) OR (A(3) AND Cin) OR (B(3) AND Cin); END PROCESS; END ARCHITECTURE behavior;

Detailed Explanation

This chunk defines the architecture of the ADDER_4BIT which is where the functionality of the entity is implemented. The PROCESS block watches changes in the inputs A, B, and Cin, executing whenever any of these inputs change. Inside the process, we perform the addition of the two inputs A and B along with the carry-in Cin to compute the Sum, which is straightforward. The carry-out Cout is computed by examining the most significant bits (MSBs) of the inputs — if any of these bits are '1', it results in a carry-out.

Examples & Analogies

Imagine this architecture like a supervisor in a factory line. The supervisor checks the input materials (A, B, Cin), processes them to create a final product (Sum), and ensures if any overflow occurs (Cout) based on certain conditions before packaging it for the customer.

Key Concepts

-

VHDL Structure: Consists of entity and architecture definitions.

-

Carry-out Logic: Defined based on the most significant bits of the inputs.

-

Testbenches: Essential for simulating designs and checking for functionality.

Examples & Applications

The VHDL entity definition for a 4-bit adder includes input declarations for two 4-bit vectors and a carry-in.

The architecture uses a process to compute the sum and carry-out based on the input conditions.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When you add two ones, a carry is begun!

Stories

Imagine two towns with 4 citizens each; but one day, they decide to unite and need to figure out how many citizens there'll be in total with some helpers!

Memory Tools

'ACES' - A for A vector, C for Carry-In, E for Entities, S for Sum Output.

Acronyms

A binary adder can be remembered as ‘A 2-Sum!’, emphasizing addition with a carry-in.

Flash Cards

Glossary

- VHDL

A hardware description language used to model electronic systems.

- Entity

Defines the inputs and outputs of a circuit in VHDL.

- Architecture

Describes the internal workings and behavior of the entity.

- Carryout (Cout)

The output that indicates an overflow beyond the highest bit in addition.

- Testbench

A VHDL or Verilog module that generates input signals for testing a design.

Reference links

Supplementary resources to enhance your learning experience.