Verification

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will discuss why verification is vital in the FPGA design process. Can anyone share what they believe happens during verification?

I think it checks if our design matches the specifications.

Exactly! Verification ensures that our implemented design behaves as intended when it finally runs on the hardware. It's like a final check before we finalize everything.

What tools do we use for verification?

Great question! We primarily use testbenches, usually created in VHDL or Verilog, to simulate inputs and evaluate the outputs of our designs.

Why is it better to do this before actual implementation?

By verifying our designs first, we can catch issues early—like logic errors or timing problems—before they become bigger headaches later on. This saves time and resources.

How do we know if the verification process was successful?

We compare the expected results against the actual outputs generated by our testbench simulations. If they match, we have successfully verified our design!

In summary, verification is essential to ensure our FPGA designs meet specifications and function correctly, and using testbenches helps facilitate this crucial step.

Creating Testbenches

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s delve deeper into creating testbenches. What do you think a testbench typically includes?

I guess it should generate input signals for the design.

Correct! A testbench provides the stimulus to our design under test and checks the result. It should also include components to monitor the outputs.

What kind of design are we testing?

Good question! For our example, we can use the 4-bit binary adder we learned about earlier. Our testbench will provide different input combinations.

Can you show us a basic structure of a testbench?

Sure! Typically, it includes the entity declaration, a component declaration of the design, signal declarations, and a process block to generate the input patterns.

What happens if our testbench results don’t match expected outputs?

That indicates an error in either the testbench or the design itself. We then need to debug and fix any discrepancies.

In conclusion, creating a thorough and effective testbench is crucial for successful verification. By utilizing this tool, we can ensure our designs operate as intended.

Verification Challenges

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's talk about some challenges we might face during verification. Can anyone think of a potential problem?

Timing issues might arise if the signals don’t meet setup and hold times.

Absolutely right! Timing violations can lead to incorrect behavior. That’s why we must pay attention to timing analysis in our designs.

What about logic errors? How do we catch them?

Logic errors are tricky but can be detected through thorough testing with various input combinations in our testbench. It’s all about covering a wide range of scenarios.

Sometimes, I find it hard to predict all possible inputs. How can we manage that?

A good practice is to use boundary values and consider special cases in your test scenarios. This helps ensure your design can handle unexpected situations.

What if the design is too complex for manual testing?

In such cases, automated testing frameworks can help. They can systematically generate test cases and verify results much faster than manual methods.

To wrap up, common verification challenges include timing issues and logic errors, but with careful test design and potentially automated tools, we can address these effectively.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In the verification phase, engineers utilize testbenches to validate the FPGA design's functionality against the initial specifications. This process helps to catch errors early, ensuring that the design meets performance and reliability requirements before final implementation.

Detailed

Verification

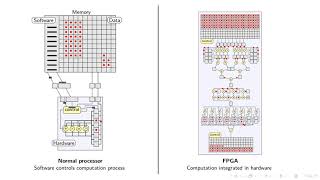

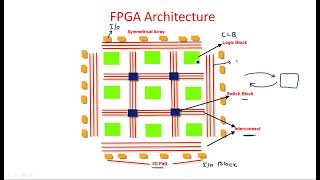

Verification is a fundamental step in the design flow of FPGA systems, focusing on ensuring that the digital circuit performs as required when implemented on the actual FPGA hardware. This section elaborates on the significance of verification, emphasizing the use of testbenches for functional validation. Engineers create these testbenches using VHDL or Verilog to generate stimulus inputs and check the outputs of the design against expected results. By thoroughly testing the design during this phase, potential issues such as logic errors, race conditions, or timing violations can be identified and rectified early in the project lifecycle, thus mitigating risks in later stages such as implementation and testing.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Purpose of Verification

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Verify the design's functionality on the actual FPGA using testbenches and real-world stimulus.

Detailed Explanation

Verification in FPGA design is the process of ensuring that the designed circuit behaves as intended when it is implemented on the hardware. This involves creating testbenches, which are specialized code segments that provide input signals and observe the outputs to confirm that the circuit operates correctly under various conditions.

Examples & Analogies

Think of verification like preparing for a play. Just as actors rehearse their lines and blocking before the final performance, engineers use testbenches to simulate the circuit behavior before deploying it to ensure everything works flawlessly on stage—here, the stage represents the FPGA.

Using Testbenches

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Testbenches are modules that generate input stimuli and check the outputs of the design.

Detailed Explanation

A testbench is an environment setup designed for testing the actual design module. It generates various sets of inputs for the circuit and verifies that the outputs match the expected results. This helps to identify any potential issues or bugs before the design is loaded onto the FPGA, allowing for corrections to be made easily and efficiently.

Examples & Analogies

Consider a testbench as a food taster in a restaurant. Before the meal is served to the guests, the taster ensures everything tastes just right. If something is off, they can suggest changes. Similarly, a testbench checks that the circuit performs accurately before it's utilized in real applications.

Significance of Real-World Stimulus

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Use real-world stimulus to simulate the circuit's operating conditions during verification.

Detailed Explanation

When verifying an FPGA design, it's crucial to use realistic input signals that mimic actual operating scenarios. This ensures that the circuit not only operates correctly under lab conditions but also in real-world situations where noise, timing variations, and other factors can affect performance.

Examples & Analogies

Imagine testing a car engine. The best way to ensure it works well is to drive it under various conditions, not just idle it in a garage. Similarly, using real-world stimulus in FPGA verification is like taking the engine on the road to see how it performs in traffic, on different terrains, and under various load situations.

Key Concepts

-

Verification: A critical step that ensures a digital circuit behaves as intended on FPGA hardware.

-

Testbench: A vital component in verification that generates stimuli and checks the output of the design.

Examples & Applications

Using a testbench for a 4-bit binary adder to verify its functionality by checking multiple input combinations against expected outputs.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Verification leads to a smooth application; check your designs before implementation.

Stories

Imagine a chef verifying a recipe by tasting it before serving; just as he ensures the dish is perfect, we verify our designs before they go live.

Memory Tools

Remember the acronym 'STAR' for verification: Simulate, Test, Analyze, Refine.

Acronyms

Use 'TVS' for Testbench

Test

Verify

Stimulate!

Flash Cards

Glossary

- Verification

The process of ensuring that the digital circuit functions correctly when implemented on hardware.

- Testbench

A simulation environment created in VHDL or Verilog to provide stimulus inputs and check outputs of a design.

- Timing Violations

Errors that occur when signal changes do not occur within specified time constraints.

- Logic Errors

Errors in a digital circuit where the output does not follow the expected logical operations.

Reference links

Supplementary resources to enhance your learning experience.