Simulation and Verification

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

The Importance of Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome class! Today, we'll explore why simulation is an essential step in our FPGA design process. Can anyone tell me what simulation does in the context of circuit design?

It checks if the circuit works as expected before we build it on the FPGA, right?

Exactly! Simulation allows us to test the design and find any potential errors. This early detection helps us avoid costly mistakes later. Remember, 'Simulate to Validate!' It's a helpful phrase to remember.

What kind of errors can simulation help us catch?

Great question! Simulation can help detect logic errors, race conditions, and timing violations. It enables us to ensure our design behaves as intended under various conditions.

Is it just about finding errors, or can we also learn something from simulation?

Good point! Simulating a design helps us understand its performance and optimize it before implementation.

In summary, simulation is a vital part of our design workflow because it helps us validate functionality and optimize our designs for better performance.

Testbenches: Writing for Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on to testbenches, who can tell me what a testbench is?

It’s like a module that sets up inputs to test the design, right?

Exactly! A testbench generates input stimuli and checks if the design outputs the expected results. Think of it as the testing ground for our circuits.

How do we create a testbench for our 4-bit adder?

We'll write a VHDL or Verilog module, instantiate our adder, and then use processes to apply different input combinations and monitor outputs. For example, we might set inputs A and B and a carry input, then check the sum and carry output.

Can we automate this? Like running several tests with one go?

Absolutely! In fact, that's best practice. You can create a series of test cases within your testbench to perform multiple tests automatically.

To recap: A testbench is critical for simulating our designs, and a well-structured testbench can help us verify the correctness of our circuits efficiently.

Analyzing Testbench Results

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we know how to create a testbench, how do we check if our design is working correctly?

We compare the output results from the simulation with the expected results, right?

Exactly! We run our testbench and observe the outputs. If the observed outputs match our expected values, then our design passes that test.

But what if they don’t match?

If they don’t match, we need to go back and debug our design. This may involve checking the code or analyzing the logic used. Remember, 'Check, Compare, Correct!' as a mnemonic to remember this debugging process.

How many tests should we run to ensure thorough verification?

Ideally, we should run tests covering all possible input combinations if feasible. More tests lead to higher confidence in our design.

In summary, analyzing testbench results is crucial for confirming the functionality of our design and identifying any issues we may have overlooked.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Simulation and verification are crucial steps in the digital design process, providing a means to test and validate circuit functionality using testbenches. By detecting potential errors early, including logic errors and timing violations, designers can ensure their circuits perform correctly before moving to implementation.

Detailed

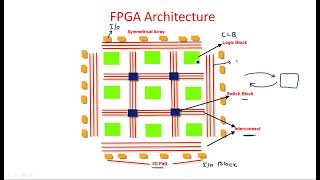

Simulation and Verification

This section emphasizes the significance of simulation and verification in the FPGA design flow. Before physically implementing a design on an FPGA, simulating it allows designers to verify the correctness of its functionality. By running a series of test inputs and evaluating the corresponding outputs, any logic errors, race conditions, or timing violations can be detected early, ensuring reliability in the implementation stage.

Key Points:

- Purpose of Simulation: The primary goal of simulation is to analyze the design's behavior in various conditions, thereby ensuring its correctness. Simulation creates a virtual environment where designers can test multiple scenarios without the risk of damaging physical hardware.

- Testbenches: Writing a testbench is an essential step in simulation. Testbenches serve as a controlled environment where specific input values can be applied to the design, and the outputs can be monitored. By employing both VHDL and Verilog, engineers can create robust testbenches that effectively validate circuit behavior.

- Examples of Testbenches: The text provides examples of VHDL and Verilog testbenches for a 4-bit adder circuit. These examples demonstrate how to stimulate the circuit with different input combinations and verify the outputs.

- Benefits of Early Verification: Identifying errors in the design phase reduces the time and cost of debugging after implementation. It also contributes to developing more efficient and reliable FPGA designs.

In summary, simulation and verification play a vital role in the design of digital circuits on FPGAs, providing the necessary checks to ensure functionality before moving towards synthesis and implementation.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Simulation

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

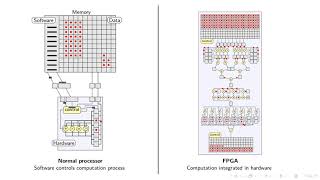

Before implementing the design on the FPGA, it is important to verify the functionality of the digital circuit using simulation. Simulating the design helps detect logic errors, race conditions, or timing violations early in the process.

Detailed Explanation

Simulation is crucial as it allows designers to test their digital circuits without physically implementing them on hardware. During simulation, you can check if the circuit behaves as expected. If issues like logic errors or timing violations are detected, they can be resolved before moving to the more costly step of implementing the circuit on an FPGA. This saves time and resources.

Examples & Analogies

Think of simulation as a dress rehearsal for a stage play. Just like actors perform their lines and blocking during a rehearsal to catch mistakes before the final performance, simulation lets engineers test their digital designs in a virtual environment before committing to the actual hardware.

Writing a Testbench for the 4-Bit Adder

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A testbench is a VHDL or Verilog module that generates input stimuli and checks the outputs of the design. Here's an example of a simple testbench for the 4-bit adder:

VHDL Testbench:

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY TB_ADDER_4BIT IS END ENTITY TB_ADDER_4BIT; ARCHITECTURE behavior OF TB_ADDER_4BIT IS SIGNAL A, B : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL Cin : STD_LOGIC; SIGNAL Sum : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL Cout : STD_LOGIC; COMPONENT ADDER_4BIT PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0); B : IN STD_LOGIC_VECTOR(3 DOWNTO 0); Cin : IN STD_LOGIC; Sum : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); Cout : OUT STD_LOGIC); END COMPONENT; BEGIN uut: ADDER_4BIT PORT MAP (A => A, B => B, Cin => Cin, Sum => Sum, Cout => Cout); stim_proc: PROCESS BEGIN A <= "0001"; B <= "0010"; Cin <= '0'; WAIT FOR 10 ns; A <= "1111"; B <= "0001"; Cin <= '1'; WAIT FOR 10 ns; A <= "0101"; B <= "1010"; Cin <= '0'; WAIT FOR 10 ns; WAIT; END PROCESS; END ARCHITECTURE behavior;

Verilog Testbench:

module TB_ADDER_4BIT; reg [3:0] A, B; reg Cin; wire [3:0] Sum; wire Cout; ADDER_4BIT uut (A, B, Cin, Sum, Cout); initial begin A = 4'b0001; B = 4'b0010; Cin = 0; #10; A = 4'b1111; B = 4'b0001; Cin = 1; #10; A = 4'b0101; B = 4'b1010; Cin = 0; #10; $finish; end endmodule

Detailed Explanation

A testbench serves as a simulator that applies different input values to the 4-bit adder and checks whether the outputs are correct. The VHDL and Verilog examples show the same concept, where the tester defines the inputs and checks the outputs for a set of predefined conditions. By running the testbench, designers can ensure that the adder works correctly under various scenarios before finalizing the design.

Examples & Analogies

Imagine a chef testing a new recipe before serving it to guests. The chef would taste the dish, refine the ingredients, and make adjustments based on feedback. Similarly, in engineering, a testbench helps 'taste' the design by identifying errors in a simulated environment before it is too late.

Stimuli and Output Checking

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Both testbenches stimulate the adder with different input values for A, B, and Cin, and verify that the output Sum and Cout are correct.

Detailed Explanation

In both VHDL and Verilog testbenches, different combinations of inputs are fed to the adder to ensure that the calculations are accurate. The expected output Sum and Cout are compared to what the adder actually produces. If they match, the design is verified as correct; if not, adjustments or debugging will be necessary.

Examples & Analogies

This process is similar to a quality control inspector testing manufactured products on an assembly line. Just as an inspector checks to see if each item meets quality standards, engineers use testbenches to verify that their circuit meets functionality standards.

Key Concepts

-

Simulation: A method for validating the functionality of digital circuits before implementation.

-

Testbench: A part of the simulation process that creates input stimuli to check the outputs.

-

Logic Errors: Bugs related to the design's logical operations that can be discovered through simulation.

-

Race Conditions: Timing issues in circuit operations that may cause unexpected behavior, detected during simulation.

-

Timing Violations: Moments when signal timings are violated, resulting in circuit failures.

Examples & Applications

A VHDL testbench for a 4-bit adder to apply different input sets and check the outputs.

A Verilog testbench equivalent that performs similar functions for the same 4-bit adder.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To design circuits that are slick, simulation’s the trick to catch any glitch.

Stories

Imagine a race where two cars start at the same time, but one takes a shortcut. The delayed car experiences a race condition, while both should finish perfectly on time in the circuit. Simulation helps prevent such racing.

Memory Tools

Simulate to Validate and Verify Early (S3VE) - Remember to check your simulation results consistently!

Acronyms

TEST - Test Every Signal Thoroughly to verify designs.

Flash Cards

Glossary

- Testbench

A module written in VHDL or Verilog that generates input stimuli and checks the outputs of the design during simulation.

- Simulation

The process of using software to model the behavior of a digital circuit and verify its correctness before physical implementation.

- Logic Error

An error in a circuit's logic design that causes incorrect outputs or behaviors.

- Race Condition

An issue in digital circuits where the output depends on the timing of events, potentially leading to unpredictable behavior.

- Timing Violation

A scenario where a signal does not meet its timing requirements, leading to potential failure in circuit operation.

Reference links

Supplementary resources to enhance your learning experience.