Best Practices for System-Level FPGA Design

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Planning the Design Architecture

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we’re going to discuss the planning of design architecture for FPGA systems. Can anyone tell me why planning is crucial?

I think it helps to know how everything will interact before we start coding.

Exactly! A well-planned architecture helps visualize data flow and control signals. Does anyone know a tool we might use for this?

Block diagrams can be useful for visualizing flow.

That's right! Using block diagrams can simplify the representation of complex interactions. Remember, a clear plan saves time in the long run. Let’s summarize this: Clear planning improves integration and efficiency. Any questions?

Using High-Level Design Abstraction

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In FPGA design, using high-level design abstractions is highly recommended. What do you think these abstractions contribute to our design process?

They probably make things easier and faster to implement, right?

Absolutely! High-level synthesis tools can accelerate the prototyping phase and allow early functional validation. Can anyone think of a specific high-level language we can use?

SystemVerilog is one that I’ve heard of.

Correct! By starting with high-level abstractions, we can focus more on functionality before making optimizations. Always remember: High-level tools lead to faster prototypes and better validation!

Testing Early and Often

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Can anyone tell me why testing during the development phase is significant?

It helps catch errors before they become bigger problems!

That's correct! Continuous testing and simulations can validate module functionality, allowing us to avoid integration headaches later. What is one strategy we can use for testing?

Using modular testbenches is a great way to isolate components.

Exactly! Modular testbenches validate individual parts of our design. To summarize: Test early, test often, and you'll save yourself a lot of trouble later on.

Optimizing for Performance

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

After confirming the functionality of our FPGA design, what should our next focus be?

Optimizing for performance?

Yes! This includes making sure our designs balance resource usage and clock speeds. Can anyone name any specific considerations we should think about during optimization?

Timing constraints are crucial, right?

Exactly right! By focusing on these optimizations, we ensure our designs perform at their best. Remember, optimization is just as vital as proving functionality!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section provides a compilation of best practices crucial for achieving success in system-level FPGA design. Key recommendations include planning the architecture, using high-level abstractions, leveraging IP cores, continuous testing, and performance optimization.

Detailed

Best Practices for System-Level FPGA Design

This section presents essential best practices involved in the successful implementation of system-level FPGA designs. By focusing on thorough planning and strategic integration of components, designers can create more efficient and reliable systems. The following practices are highlighted:

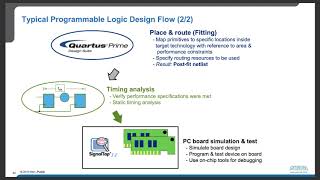

- Plan the Design Architecture: Clear definition of the overall system architecture is vital. This includes understanding how subsystems and IP cores will interact. Utilizing block diagrams can visualize data flow and control signals effectively.

- Use High-Level Design Abstraction: High-level abstractions, such as SystemVerilog or high-level synthesis tools, should be used to develop prototypes swiftly. This allows for quick validation of functionality before delving into detailed low-level optimizations.

- Leverage IP Cores: Designers should utilize standard IP cores as much as possible to accelerate development time. These cores have already been tested and optimized for implementation in FPGAs, reducing the risk of design errors.

- Test Early and Often: Continuous simulation and testing throughout development is vital. Employing modular testbenches allows for validation of individual components prior to full system integration, helping to identify issues early.

- Optimize for Performance: After functionality confirmation, the focus should shift to performance optimization. This involves balancing resource usage with clock speeds and timing constraints to achieve the best performance outcomes.

In summary, these best practices aim to streamline the design and integration processes while enhancing the overall quality of FPGA-based systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Design Architecture Planning

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Plan the Design Architecture: Begin by clearly defining the overall system architecture, including the interaction between different subsystems and the IP cores. Use block diagrams to visualize the flow of data and control signals.

Detailed Explanation

In this chunk, the emphasis is on the importance of planning the design of your FPGA system right from the start. Before diving into coding, you should sketch out how your entire system will look and operate. This includes identifying how different components will communicate with each other and using visual aids like block diagrams to represent these interactions. By laying out your design architecture in advance, you can identify potential issues early and ensure that your different components, such as IP cores, will fit together seamlessly.

Examples & Analogies

Think of planning your FPGA design like planning a road trip. Before you hit the road, you would map out your route, noting all the stops along the way, just like you plan out your system architecture. If you know where each rest stop (component) is, you can avoid getting lost and ensure that you reach your destination efficiently.

High-Level Design Abstraction

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Use High-Level Design Abstraction: Start with high-level abstractions (e.g., using SystemVerilog or high-level synthesis tools) to quickly create prototypes and verify functionality before implementing low-level optimizations.

Detailed Explanation

This section discusses the advantages of starting your FPGA design with high-level abstractions. Using languages like SystemVerilog or high-level synthesis tools allows you to develop and test your design at a higher level, which can speed up the initial phases of your project. By creating prototypes early on, you can ensure that your design functions as expected before getting into more complex, low-level optimizations that may complicate matters. This method also facilitates quicker iterations, allowing you to refine your design based on test results.

Examples & Analogies

Consider this approach like drafting a blueprint for a building. Before constructing a detailed model, you sketch out the overall design. This way, you can quickly identify design flaws or layout issues and fix them before committing to the final build. It saves time and resources in the long run.

Leverage IP Cores

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Leverage IP Cores: Use standard IP cores wherever possible to reduce development time. These cores have been tested and optimized for FPGA implementations.

Detailed Explanation

This chunk highlights the importance of making full use of available standard IP cores during your FPGA design process. IP cores are pre-designed modules that have been thoroughly tested and optimized, which means you can save substantial time and effort by incorporating them into your project instead of designing everything from scratch. By leveraging these resources, you can ramp up your productivity and focus on the unique aspects of your design.

Examples & Analogies

Think of leveraging IP cores like using ready-made furniture instead of building everything in your home from raw materials. When you choose pre-assembled shelving units or tables, you spend less time on construction and can quickly create a functional living space. Similarly, using IP cores allows you to set up essential functionalities without reinventing the wheel.

Testing Early and Often

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Test Early and Often: Continuously simulate and test your design throughout the development process. Use modular testbenches and system-level simulations to validate each component before integration.

Detailed Explanation

This section emphasizes the critical practice of continuous testing during the development cycle of an FPGA design. By simulating and testing your design at multiple stages, especially using modular testbenches, you can verify that each part of your system works as intended before bringing everything together. This iterative testing approach helps in identifying and correcting errors early, which can significantly reduce complications during final integration.

Examples & Analogies

Testing early and often is akin to checking the quality of ingredients while cooking a meal. If you taste the dish as you prepare it, you can adjust the seasoning or fix issues before serving. By validating small portions of your design continuously, you ensure that each component is ‘seasoned’ correctly before the final presentation.

Performance Optimization

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Optimize for Performance: After confirming functionality, focus on optimizing the design for performance by balancing resource usage, clock speeds, and timing constraints.

Detailed Explanation

This final chunk discusses the importance of optimizing your FPGA design's performance once you have confirmed that it functions as intended. This involves fine-tuning various aspects such as resource usage, clock speeds, and timing constraints. Optimization ensures that your design not only meets functional requirements but also performs efficiently under operational conditions. This step is crucial for applications where speed and responsiveness are key factors.

Examples & Analogies

Optimizing for performance can be compared to tuning a musical instrument. After you have learned to play a song correctly, you spend time adjusting the tuning of each string to ensure the music sounds its best. Similarly, once your design works, you refine it to ensure it operates at maximum efficiency, making it 'sing' in terms of performance.

Key Concepts

-

Design Architecture Planning: Critical for ensuring a clear understanding of component interactions and system flow.

-

High-Level Abstraction: Speeds up prototype development and validation.

-

Testing and Validation: Continuous testing can identify issues early in the design phase.

-

Performance Optimization: Enhances efficiency by balancing resource usage with performance requirements.

Examples & Applications

Creating a block diagram to visualize the interaction between several IP cores and subsystems in an FPGA design.

Using SystemVerilog to prototype a system, allowing quick testing before moving to low-level designs.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Plan your design, it's the key, / High-level tools let ideas flow free.

Stories

Imagine two builders. One sketches out a clear blueprint before starting, while the other jumps in without a plan. The first builder constructs a sturdy house that meets needs, while the second struggles with last-minute changes.

Memory Tools

PTHO: Plan, Test, High-level abstraction, Optimize.

Acronyms

P.T.H.O

Planning

Testing

High-level design

Optimization.

Flash Cards

Glossary

- IP Cores

Pre-designed, reusable blocks of logic that implement specific functionalities in FPGA designs.

- HighLevel Abstraction

Techniques that simplify the design process by allowing for higher-level programming languages or synthesis tools.

- Modular Testbenches

Isolated testing frameworks used to validate the functionality of smaller design components in FPGA systems.

- Performance Optimization

The process of refining a design to enhance its resource utilization and timing characteristics.

Reference links

Supplementary resources to enhance your learning experience.