Example: Integration of UART and FIFO IP Cores

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Selecting IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're going to look at selecting IP cores for integration. Why is it important to choose the right IP cores?

Because the choice affects the system’s performance and capabilities, right?

Exactly! Selecting the right cores ensures that we meet our system requirements effectively. Can you think of some parameters we need to consider?

We should think about functionality, performance, and resource utilization.

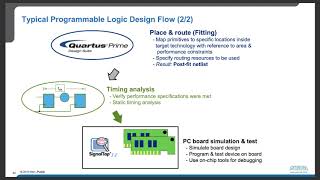

Great points! Remember, FPR design tools like Vivado or Quartus aid in configuring these cores through wizards, which simplifies the process. Let’s remember the acronym FPR - Functionality, Performance, Resources.

Got it! FPR!

To sum up, selecting the right cores involves a thorough understanding of our needs, balancing performance with available resources.

Configuring Interfaces

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we've selected our UART and FIFO cores, how do we connect them?

We need to configure their interfaces properly, right?

Yes! This involves mapping the TX and RX pins of the UART to the input and output of the FIFO. Why do you think this mapping is crucial?

If we don’t map them correctly, the data won’t flow as intended.

Precisely! Misconfiguration can lead to data loss. Let's visualize this: TX from UART going to FIFO Input is an important connection to remember - think of it as a pipe carrying data.

I like that visualization. A data pipe!

Wrapping up, correct configuration and mapping allow for seamless data communication between IP cores and form a stable foundation for our design.

Connecting Control Signals

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Connecting control signals is the next step. What types of control signals do we need to implement for our UART and FIFO?

Reset, clock, and enable signals for read/write operations!

Exactly! Connecting these signals ensures that both cores operate correctly. Can anyone suggest why timing is so crucial for these signals?

Because if they're not synchronized, data could be written or read at the wrong times, causing errors.

Right! Think of it like a well-rehearsed orchestra; every musician has to play in sync to create beautiful music. In our case, synchronization prevents data errors.

That metaphor helps a lot!

In summary, timely connections of control signals are essential for managing the operations of our IP cores and ensuring smooth data transfer.

Simulating the System

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

The final step involves simulating the system. Why do we simulate before physical implementation?

To catch any issues or bugs related to data transmission before building the hardware!

Exactly! A simulation allows us to analyze the interactions between our UART and FIFO. How can we conduct a simulation?

Using a testbench to create conditions that mimic real-world scenarios.

Yes! This step is vital in validating our design. Remember to keep a checklist of what to test, such as data integrity and timing, so that nothing is overlooked.

I’ll definitely create a checklist for my designs!

Wrapping up, simulating allows us to verify functionality and refine performance, ensuring a robust IP core integration.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the integration process of two commonly used IP cores: UART for serial communication and FIFO for buffering data. The steps include selecting and configuring the IP cores, mapping their interfaces, connecting control signals, and simulating the system to ensure proper data transmission.

Detailed

Integration of UART and FIFO IP Cores

In the realm of FPGA designs, the integration of IP cores plays a crucial role in achieving effective communication and data management. This section presents a specific example of integrating two widely used IP cores: the UART (Universal Asynchronous Receiver/Transmitter) and FIFO (First In, First Out) buffer.

Key Steps in Integration:

- Select UART and FIFO IP Cores: Utilize the configuration wizard in your FPGA design tool to choose and configure these cores. Key parameters such as data width for UART, baud rate, and FIFO buffer size must be defined to tailor the cores to the design's requirements.

- Configure Interfaces: Careful mapping of the UART's transmit (TX) and receive (RX) pins to the FIFO's input and output is essential for ensuring correct data flow between the cores. This configuration is vital as it establishes the data path.

- Connect Control Signals: Ensure that all necessary control signals, including reset, clock, and read/write enables for the FIFO, are accurately linked to the respective components within the system. This step is crucial for maintaining synchronization and functionality of the integrated system.

- Simulate the System: Using a testbench, the developed system can be simulated to ensure that the UART and FIFO cores interact as expected. Simulations help identify potential data transmission issues and buffer management concerns before the hardware implementation, making it a vital part of the development process.

Through this example, we see how integrating UART and FIFO IP Cores contributes to the broader objective of developing robust, efficient, and scalable FPGA-based systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Selecting UART and FIFO IP Cores

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Select UART and FIFO IP Cores: Use the configuration wizard in the FPGA tool to select and configure the UART and FIFO cores. Set the UART data width, baud rate, and FIFO buffer size.

Detailed Explanation

In this step, we begin by choosing the UART and FIFO IP cores from the IP catalog within the FPGA design tool. The configuration wizard will guide you through the selection process. You need to set specific parameters for both cores, including:

- UART Data Width: This determines how many bits can be transmitted or received at once. Common data widths are 8 bits or 16 bits.

- Baud Rate: This defines the speed of the communication (e.g., how many bits are transmitted per second). Typical baud rates are 9600, 115200, etc.

- FIFO Buffer Size: This is the amount of data the FIFO can hold. A larger FIFO can accommodate more data but may use more resources on the FPGA. Choosing appropriate values based on the application requirements is critical to ensure efficient data flow.

Examples & Analogies

Imagine you are setting up a postal system where data represents letters. The UART is like the postal service that delivers letters, and the FIFO is the sorting facility that temporarily holds letters before they are sent out. By configuring which types of letters (data width), how fast they should be delivered (baud rate), and how many letters can be held at once (FIFO size), you help streamline communication and avoid bottlenecks.

Configuring Interfaces

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Configure Interfaces: Map the UART TX and RX pins to the FIFO input and output respectively, ensuring proper data flow.

Detailed Explanation

Once the IP cores are selected, the next step is to establish clear connections between them. This step involves mapping the pins of each core so they can communicate effectively:

- UART TX Pin: This is the Transmit pin of the UART, which sends data to another device. This pin needs to be connected to the FIFO Input so that data sent from UART flows into the FIFO buffer.

- UART RX Pin: This is the Receive pin of the UART, which accepts incoming data. This pin should be connected to the FIFO Output, allowing the FIFO to send stored data out when needed.

The correct mapping ensures the data sent by the UART gets stored in the FIFO properly for later processing.

Examples & Analogies

Think of this mapping as arranging how different departments in a company communicate. The UART TX is like a department sending out meeting notes (data) to the storage department (FIFO input). The FIFO then holds these notes until required for a project (FIFO output when data is retrieved). Ensuring the correct routing of these notes prevents confusion and keeps everything running smoothly.

Connecting Control Signals

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Connect Control Signals: Connect the control signals like reset, clock, and FIFO write/read enable to the appropriate logic in the system.

Detailed Explanation

Control signals are crucial for the operation of the UART and FIFO cores. This step ensures that all necessary control signals are connected properly:

- Reset Signal: This signal initializes the cores. When activated, it clears any data stored and sets the cores to a known state.

- Clock Signal: Synchronization between the cores is provided by this signal. It ensures that both the UART and FIFO operate in time with each other. Without synchronized clocks, data may not be transferred correctly.

- FIFO Write/Read Enable Signals: These controls dictate when data can be written to or read from the FIFO. It's crucial to ensure that these signals are routed to the suitable logic components that enable proper operation of the FIFO.

Connecting these signals accurately is essential for reliable communication between the UART and FIFO cores.

Examples & Analogies

Imagine a theater production as an analogy. The reset signal is like the cue that tells actors to start the play from the beginning. The clock signal is like the conductor keeping time for the musicians; everyone needs to follow along to ensure the show runs smoothly. The FIFO write/read enable signals are like the director's instructions on when actors should start or stop performing. If everyone is aligned and aware of their timing, the show will be a success!

Simulating the System

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Simulate the System: Use a testbench to simulate the interaction between the UART and FIFO, checking for correct data transmission and buffer management.

Detailed Explanation

Simulation is the final step in verifying system functionality before hardware implementation. In this step, a testbench is created, which acts as a controlled environment where you can test the design:

- The testbench generates specific input signals to the UART and checks if the data is appropriately buffered in FIFO.

- It tests various scenarios, such as sending data through UART and confirming if FIFO holds this data correctly and allows for reading when needed.

- It's vital to assess performance metrics like data loss, timing delays, and proper handling of data overflows.

This step is critical as it helps uncover potential issues that could arise during actual operations on the FPGA.

Examples & Analogies

Think of the simulation as a dress rehearsal for the theater production. The cast and crew run through the entire play to ensure everything works as planned. The director watches closely for any mistakes or issues that might need fixing. If everything operates smoothly during rehearsal (simulation), the show (actual implementation) is likely to go well!

Key Concepts

-

UART: An essential component for serial communication in FPGA designs.

-

FIFO: A buffering system crucial for managing data flow between IP cores.

-

Control Signals: Essential for coordinating operations between UART and FIFO.

-

Testbench: A tool for simulating system interactions prior to hardware implementation.

Examples & Applications

Integrating UART with FIFO helps to manage the flow of data during serial communication, showcasing how these IP cores work in concert to ensure data is handled efficiently.

By utilizing configuration tools, designers can set parameters such as baud rate and buffer size to optimize the performance of the integrated cores.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

For data to flow, like a smooth river, use FIFO for buffering, it works like a giver.

Stories

Imagine a water pipeline. The FIFO is the tank that stores water until it's sent through the pipe (UART) to your home (the processing unit).

Memory Tools

Remember 'SR - Signal Routing' for the key control signals: Start and Reset.

Acronyms

USE for integration steps

Understand

Select

Execute.

Flash Cards

Glossary

- UART

Universal Asynchronous Receiver/Transmitter; a hardware device for asynchronous serial communication.

- FIFO

First In, First Out; a type of buffer used to manage data flow in systems.

- Control Signals

Signals used to coordinate and manage the operations of components within a circuit.

- Testbench

A simulation environment used to verify the functionality of a design by creating input conditions.

- Configuration Wizard

A tool in FPGA design software that guides users through the setup and configuration of IP cores.

Reference links

Supplementary resources to enhance your learning experience.