Introduction to IP Cores in FPGA Design

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will explore what IP cores are. Can anyone tell me what you think an IP core is?

Is it a kind of module used in FPGA designs?

Exactly! IP cores are pre-designed and reusable logic blocks that implement specific functionality. They are crucial for accelerating the development of FPGA-based systems.

What kind of functionalities do they provide?

Great question! IP cores can handle various functions like communication protocols and memory management. Remember the acronym **C-MAP**: Communication, Memory, Arithmetic, and Processing for the kinds of functionalities.

Why is it advantageous to use IP cores instead of designing everything from scratch?

Using IP cores saves time and reduces the complexity of our designs, enabling us to focus on integration and validation. It makes the development process much more efficient!

Can you give an example of an IP core?

Sure! A UART controller is a common soft IP core used for serial communication. Let's summarize: IP cores accelerate FPGA design, come in various forms, and are vital for system complexity.

Types of IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's differentiate between hard and soft IP cores. Who can tell me what a hard IP core is?

Is it one that’s fixed in the FPGA silicon?

That's correct! Hard IP cores are pre-designed blocks that provide high performance. Examples include memory controllers. On the other hand, soft IP cores are described in HDL. Can anyone share an example of a soft IP core?

A UART controller?

Exactly! Soft IP cores offer more flexibility but may sacrifice some performance. To help remember, think **HARD is fixed; SOFT is flexible**.

So, what would be some considerations when choosing between them?

You have to consider performance, flexibility, and resource allocation. Balancing these is key to efficient FPGA design.

Examples of IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's discuss some common types of IP cores. Who can name a specific core used for computation?

How about a microprocessor core?

Exactly! Processor cores are one type. We also have IP cores for communication protocols like SPI and Ethernet. Remember **PEM**: Processors, Ethernet, Memory for their categories.

What about security? Are there IP cores for that too?

Yes, there are! Security IP cores include AES for encryption and SHA for hashing. These are essential in modern designs.

So, could we integrate a UART for communication alongside a DSP core for signal processing?

Absolutely! Combining different IP cores allows us to create versatile and functional designs.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section introduces intellectual property (IP) cores as crucial components in FPGA design, enabling faster and more efficient development of complex systems. It discusses the classification of IP cores into hard and soft categories, highlighting specific examples and their functionalities.

Detailed

Introduction to IP Cores in FPGA Design

Intellectual Property (IP) cores are essential elements in FPGA design, acting as pre-designed and reusable logic blocks or modules that implement distinct functionalities—ranging from communication protocols to memory controllers and arithmetic operations. These cores expedite the development process, allowing designers to focus on higher-level system integration rather than reinventing each component from scratch.

IP cores are generally classified into two main categories: hard IP cores, which are fixed and incorporated directly into the FPGA's silicon, thus offering high performance and low latency; and soft IP cores, which are described with hardware description languages (HDL) like VHDL or Verilog and synthesized within the FPGA's fabric, allowing for greater flexibility but potentially lower performance. Examples of hard IP cores include memory controllers and DSP blocks, while soft IP cores can include UART controllers and custom logic functions.

In this chapter, we will delve into various types of IP cores, tools for their integration, and best practices for system-level design, emphasizing how these cores enable the creation of large-scale, complex FPGA-based systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

What are IP Cores?

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Intellectual Property (IP) cores are pre-designed, reusable logic blocks or modules that implement specific functionality, such as communication protocols, memory controllers, or arithmetic functions.

Detailed Explanation

IP cores are essentially pre-packaged components that can be used in FPGA designs. They come with defined functionalities, meaning designers do not need to build these elements from scratch. Rather, they can focus on integrating these established modules into their systems, which speeds up development and enhances reliability.

Examples & Analogies

Think of IP cores like buying prefabricated furniture instead of building everything from raw materials. When you purchase a ready-to-assemble piece, you save time and effort—as it’s already designed to function seamlessly. This is similar to how IP cores help FPGA designers by providing ready-made solutions for common tasks.

Importance of IP Cores in FPGA Design

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

These IP cores are essential for accelerating the development of complex FPGA-based systems, as they save time and reduce the need for designers to create every component from scratch.

Detailed Explanation

The use of IP cores significantly streamlines the design process. Instead of starting from zero, FPGA designers can utilize these ready-made blocks to quickly assemble a larger system. This acceleration not only shortens the development timeline but also reduces errors since IP cores are tested and validated components.

Examples & Analogies

Imagine trying to build a complex machine from individual components like bolts and gears. You could certainly do it, but it would take a long time and require a deep understanding of every part. Using IP cores is like using a kit; all the pieces are designed to work together, which makes building the final product faster and often easier.

Overview of Chapter Content

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

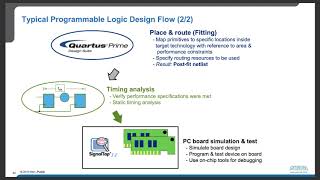

In this chapter, we will explore how IP cores are integrated into FPGA designs and how system-level design concepts can be applied to develop large-scale, complex FPGA-based systems. We will discuss the different types of IP cores available, the tools for integrating them, and best practices for system-level design.

Detailed Explanation

This chapter will guide you through the landscape of using IP cores in FPGA design, highlighting not only their types but also how to effectively integrate them into complex systems. You'll learn about the tools available for integrating these cores as well as strategies to ensure they work optimally within a broader system design context.

Examples & Analogies

Think of this chapter as a roadmap for a journey. It outlines the route you’ll take (integrating IP cores), what you'll see along the way (types and tools), and tips for smooth travel (best practices) to help you reach your destination of building a complex FPGA system more efficiently.

Key Concepts

-

Intellectual Property Cores: Reusable building blocks in FPGA design.

-

Hard IP Cores: Fixed blocks for high performance.

-

Soft IP Cores: Flexible cores defined in HDL.

-

IP Core Integration: Essential for building complex systems.

Examples & Applications

A UART controller for effective serial communication in digital systems.

A DSP core used for implementing FFT algorithms in signal processing.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

IP cores, oh what a find! Logic blocks, all designed!

Stories

Once, in a land of circuits, lived hard and soft IP cores. Hard ones were like mighty knights, strong and fixed; soft ones were clever wizards, flexible and adaptable.

Memory Tools

Remember the core types: H for Hard, F for Flexible (Soft), P for Performance, and F for Flexibility.

Acronyms

C-MAP for IP functions

Communication

Memory

Arithmetic

Processing.

Flash Cards

Glossary

- IP Core

A reusable logic block or module that implements specific functionality in FPGA designs.

- Hard IP Core

Pre-designed hardware blocks that are fixed and implemented directly in the silicon of the FPGA.

- Soft IP Core

Cores described using HDL (VHDL or Verilog) and synthesized into the FPGA's fabric for flexibility.

- UART

Universal Asynchronous Receiver/Transmitter, a common soft IP core for serial communication.

- DSP Core

Digital Signal Processing core, used for mathematical operations and signal manipulation.

Reference links

Supplementary resources to enhance your learning experience.