Modular Design Approach

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Top-Level Module

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to learn about the top-level module in our FPGA designs. The top-level module serves as the highest-level design entity that connects all sub-modules. Can anyone tell me why we need such a module?

Is it to manage all the different parts and make sure they work together?

Exactly! It’s like the conductor of an orchestra, ensuring each instrument plays its part in harmony. Now, how do you think this compares to a traditional programming approach?

In programming, we also have a main function that connects everything. So, it's pretty similar!

Great analogy! Let’s remember that—both are central control points facilitating interaction among different components. And what do you think is the benefit of having organized sub-modules?

It simplifies troubleshooting and lets you reuse parts then?

Correct! Modular design allows us to isolate problems effectively, making debugging less of a hassle. Let’s summarize: the top-level module connects sub-modules, facilitates interaction, and is similar to the main function in programming.

Utilizing Sub-modules

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s talk about sub-modules. What do you think makes dividing a design into smaller modules beneficial?

It must make it easier to manage complex designs, right?

Exactly! Smaller modules mean you tackle one piece at a time. Why is this crucial for large FPGA designs?

Because we can focus on one functionality without getting overwhelmed by everything at once!

Correct! This allows for better organization and reusability. So, if you had to explain this to someone new, how would you describe the modularity concept?

I’d say it’s about creating separate pieces that can be reused and tested independently, like a set of building blocks.

Great analogy! Each block represents a module that can fit together, forming a solid design. Remember, modular design promotes efficiency and clarity.

IP Core Reusability

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's now address the concept of IP core reusability in our designs. Why do you think it's important?

Reusing them can save time since they are already developed and tested!

Exactly! And can you think of how this impacts project timelines?

It could significantly shorten development time, allowing us to focus on unique aspects of our design.

Right! Utilizing standardized IP cores can also enhance performance because they are optimized for specific functions. What’s a good memory technique to remember the benefits of IP core reusability?

How about the acronym RACE? Reusability, Acceleration of Development, Consistency, and Efficiency.

Fantastic! RACE encapsulates the advantages of IP core reuse in a memorable way. Let’s wrap up with understanding that through modularity and reusability, we can create powerful design ecosystems.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This approach breaks down complex FPGA designs into manageable sub-modules, each of which handles specific functionalities. This modularity not only simplifies the design process but also fosters reusability and easier debugging of components, which are critical in developing effective FPGA-based systems.

Detailed

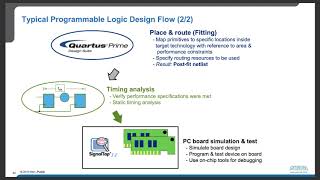

Modular Design Approach

The Modular Design Approach in FPGA system design emphasizes the organization of design components into a hierarchy of modules. At the highest level, a Top-Level Module integrates all the sub-modules, which could include various IP cores, custom logic, and memory elements.

Key Points:

- Top-Level Module: This module serves as the central connection point for all sub-modules, essentially acting as the main controller of the system.

- Sub-modules: The design is divided into smaller, reusable modules, each responsible for distinct functionalities. This method enhances maintainability and makes debugging easier, thereby streamlining the development process.

- Reusability of IP Cores: By utilizing standard IP cores consistently across different designs, developers can significantly reduce development time and increase efficiency, as these cores are often well-tested and optimized for FPGA implementations.

Overall, the Modular Design Approach ensures a structured methodology for creating FPGA systems, which is essential for managing complexities associated with modern electronic designs.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Top-Level Module

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The top-level module is the highest-level design entity that connects all the sub-modules, including IP cores, custom logic, and memory elements.

Detailed Explanation

The top-level module is the most comprehensive part of your FPGA design. It synthesizes everything into a single, cohesive unit. Think of it as the captain of a ship. Just as a captain coordinates the crew and ensures everything functions smoothly, the top-level module connects different smaller modules (or sub-modules) that perform specific functions. By using a top-level module, you ensure that all components can interact with each other correctly.

Examples & Analogies

Imagine a large orchestra. The conductor (top-level module) coordinates various sections like strings, woodwinds, and brass. Each section plays its part (sub-modules) but together creates a harmonious piece of music (the final FPGA design). Without a conductor, the music would be chaotic, just as a design without a top-level module would likely not function correctly.

Sub-modules

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Break the design into smaller, reusable modules, each responsible for a specific functionality. This modular approach simplifies the design process, improves maintainability, and facilitates debugging.

Detailed Explanation

Sub-modules are smaller parts of your overall design that handle specific tasks. By breaking your design into these manageable units, you make it easier to work on each part independently. This is similar to creating a jigsaw puzzle where each piece (sub-module) fits into the bigger picture. Modularity simplifies the design because if there's an issue, you can focus on just one sub-module instead of the entire design. It also improves maintainability because you can update or reuse a sub-module in other designs without starting from scratch.

Examples & Analogies

Consider an automobile factory. Each department works on specific car parts—chassis, engines, painting, etc. If there's a problem with the engine, only that department is involved in troubleshooting, allowing for quick fixes and modifications without halting the entire production.

IP Core Reusability

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Use standard IP cores across different designs to ensure reusability and reduce development time.

Detailed Explanation

IP core reusability is about taking pre-designed blocks of logic (IP cores) and using them in different projects without modification. This is a crucial advantage in FPGA design because it saves time and resources. When you find an IP core that meets your needs, you can simply integrate it into various designs. This avoids reinventing the wheel and allows you to focus on the unique aspects of your current project.

Examples & Analogies

Think of a tool like a power drill. If a builder has a reliable drill, they don’t need to invent a new one for each building project. Instead, they can use that same drill across various constructions, making their work more efficient and consistent.

Key Concepts

-

Modular Design: A structured approach in FPGA design that divides the overall design into manageable units.

-

Top-Level Module: The primary module that integrates all other sub-modules, facilitating interaction.

-

Sub-modules: Individual components of the overall design, enhancing maintainability and reusability.

-

IP Core Reusability: The practice of utilizing pre-designed IP blocks in multiple designs to enhance efficiency.

Examples & Applications

Implementing a UART communication module as a reusable sub-module in various designs.

Designing a memory controller as an IP core to be integrated across different FPGA projects.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

A top-level design is like a chef’s meal, / Sub-modules are ingredients, each with appeal.

Stories

Imagine building a Lego castle. The top-level is the base, and each block is a sub-module, making it easier to add or remove sections.

Memory Tools

Remember the FLOSS method: Functionality, Layout, Organization, Simplicity, Sub-modules to visualize designing an FPGA structure.

Acronyms

MATRIX

Modularity

Reusability

Affordability

Time-saving

Reliability

Improves efficiency

eXcellence.

Flash Cards

Glossary

- TopLevel Module

The highest-level design entity that connects and coordinates all sub-modules in an FPGA design.

- Submodules

Smaller, reusable modules within a design, each responsible for specific functionalities.

- IP Cores

Pre-designed, reusable logic blocks in FPGA design that provide specific functionalities, such as processors or communication interfaces.

- Reusability

The ability to use modules or cores in multiple designs, reducing development time and effort.

Reference links

Supplementary resources to enhance your learning experience.