Conclusion

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

The Importance of IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're going to discuss why IP cores are vital in FPGA designs. Who can tell me what we learned about IP cores?

IP cores help speed up the design process by providing pre-designed modules.

Great! That's correct. Using IP cores can save designers significant time, especially for complex functions. Can anyone mention a specific type of IP core?

How about communication protocols like UART?

Exactly, UART is one example of a communication protocol IP core. Remember, we can use the acronym 'HSC' for Hard, Soft, and Custom to remember the core types. Can someone explain the difference between hard and soft IP cores?

Hard IP cores are fixed in the FPGA silicon, while soft IP cores are flexible and can be synthesized.

Perfect! Let's summarize: IP cores enhance design efficiency, reduce development time, and can be high-performance or flexible. Moving on!

System-Level Design Practices

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's discuss system-level design practices. Why do you think these practices are necessary?

They help manage complexity when integrating multiple IP cores and custom logic.

Exactly! System-level design helps in optimizing resource usage and ensuring efficient communication. Who remembers a key practice we discussed?

Planning the architecture and using modular design.

Right! By breaking down the design into modular components, we can streamline development and facilitate debugging. Summarizing this session, modular design and careful planning are crucial in managing complex FPGA systems.

FFinal Thoughts on IP Cores and System Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

As we wrap up, how do you see the integration of IP cores influencing future FPGA designs?

It will likely lead to faster and more efficient designs as technology evolves.

Absolutely! With cutting-edge technology, the reusability and efficiency of IP cores will enhance FPGA capabilities. Can anyone share a takeaway from this chapter?

That by using IP cores effectively, we can achieve high performance while simplifying our design process.

Great takeaway! Always remember the flexibility and scalability that IP cores introduce into designs. Let's summarize everything: IP cores combined with robust system-level design enable efficient, scalable FPGA systems.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In the conclusion of this chapter, the benefits and strategic integration of IP cores are highlighted, showing how they streamline the design process for FPGA-based systems. Effective system-level design practices are essential for utilizing these cores efficiently.

Detailed

Conclusion

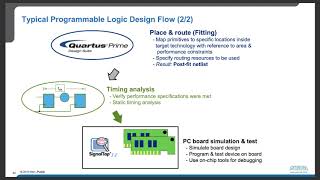

In this chapter, we explored the integration of IP cores and system-level design for FPGA-based systems. IP cores offer significant advantages in terms of design speed, reusability, and performance, and integrating them into a system requires a solid understanding of the FPGA’s architecture and design flow. System-level design practices ensure that these cores can be used efficiently and effectively to build complex, high-performance systems. By following the integration process and best practices outlined in this chapter, you can develop FPGA systems that meet your specific design requirements, offering flexibility and scalability for a wide range of applications.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of IP Cores and System-Level Design

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this chapter, we explored the integration of IP cores and system-level design for FPGA-based systems.

Detailed Explanation

This part of the conclusion summarizes the main focus of the chapter, which is on how IP cores and system-level design practices come together in FPGA systems. It emphasizes that understanding these concepts is crucial for successful FPGA implementation.

Examples & Analogies

Think of building a complex Lego structure. Just like you must understand how different Lego pieces fit together to create a masterpiece, understanding IP cores and system design helps you build efficient FPGA-based systems.

Benefits of Using IP Cores

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

IP cores offer significant advantages in terms of design speed, reusability, and performance.

Detailed Explanation

This chunk highlights the benefits of using IP cores. They save time because designers can use ready-made components instead of creating everything from scratch. Furthermore, they promote reusability across different projects, which can lead to faster development cycles and improved system performance.

Examples & Analogies

Using IP cores is like having pre-assembled furniture. It saves you the time and effort of building everything yourself, allowing you to focus on personalizing your space instead.

Requirements for Integration

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Integrating them into a system requires a solid understanding of the FPGA’s architecture and design flow.

Detailed Explanation

In this section of the conclusion, it is explained that successful integration of IP cores into an FPGA design demands a deep understanding of the underlying architecture and the overall design workflow. Knowledge of how the FPGA operates and how different components interact is essential for optimal performance.

Examples & Analogies

Imagine trying to assemble a complicated piece of machinery without knowing how each part works. Just like you need to understand the function of each component for proper assembly, you must grasp the FPGA architecture for effective IP core integration.

System-Level Design Practices

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

System-level design practices ensure that these cores can be used efficiently and effectively to build complex, high-performance systems.

Detailed Explanation

This part emphasizes that applying proper system-level design practices is crucial for using IP cores effectively. It involves structuring the design thoughtfully and utilizing best practices to achieve high performance in the final system.

Examples & Analogies

Consider organizing a team project: the success of the project relies on good planning, clear roles, and efficient communication. Similarly, system-level design practices streamline the integration of IP cores for optimal results.

Final Thoughts

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

By following the integration process and best practices outlined in this chapter, you can develop FPGA systems that meet your specific design requirements, offering flexibility and scalability for a wide range of applications.

Detailed Explanation

The conclusion wraps up by reinforcing that adherence to the outlined processes and best practices leads to the successful development of FPGA systems tailored to meet specific needs, highlighting the versatility and exponential potential of these systems in various applications.

Examples & Analogies

Just like a chef following a recipe can create a dish that caters to specific tastes, following the integration process and best practices helps in crafting FPGA systems that meet unique project needs.

Key Concepts

-

Integration of IP Cores: Essential for efficient FPGA design.

-

System-Level Design: A structured approach for building complex FPGA systems.

Examples & Applications

Implementing a UART IP core for communicating with external sensors.

Using a DSP IP core to process audio signals in real-time.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

IP cores speed things up, no need to stop; they help us at the top!

Stories

Imagine building a castle (your FPGA) using prefabricated blocks (IP cores). Each block gives strength, and they fit perfectly together—saving time and glorious in structure.

Memory Tools

Use 'PRIME' to remember: Plan, Reuse, Integrate, Manage, and Execute for system-level designs.

Acronyms

Remember 'HSC' for Hard, Soft, and Custom cores when discussing IP cores.

Flash Cards

Glossary

- IP Cores

Pre-designed, reusable logic blocks in FPGAs that implement specific functionalities.

- Hard IP Cores

Fixed hardware blocks implemented directly in the FPGA silicon.

- Soft IP Cores

Logic described using HDL that can be synthesized into the FPGA fabric.

- Resource Utilization

The impact of IP cores on the overall resources of the FPGA, like logic blocks and I/O.

Reference links

Supplementary resources to enhance your learning experience.