Interface and Communication Protocols

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Communication Protocols

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will talk about communication protocols, crucial for interfacing different components in FPGA designs. Can anyone define what a communication protocol is?

Isn't it like a set of rules that allows different devices to communicate?

Exactly! Communication protocols are indeed the rules governing data exchange between devices. They ensure smooth interaction among various subsystems.

What are some examples of these protocols?

Good question! Some major examples include SPI, UART, and I2C. Let’s remember them with the acronym **SUI**: S for SPI, U for UART, and I for I2C. This will help you recall them easily!

How do these protocols differ from one another?

Great point! We'll discuss their differences shortly. Remember, understanding these protocols is essential for effective communication in system-level design.

AXI Interface

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s delve into the AXI (Advanced eXtensible Interface). Can anyone tell me why AXI is popular among FPGA designers?

I think it’s because it supports high performance and low latency, right?

Exactly! AXI is designed for high-bandwidth applications, making it advantageous in larger designs. It's critical for transferring data swiftly between IP cores. Can anyone describe its primary features?

I know it offers burst transfers and multiple data channels.

Correct! Burst transfers allow multiple data items to be sent in a single transaction, optimizing performance. Remember to consider AXI when designing high-performance FPGA systems!

Avalon Interface

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s talk about the Avalon interface. Why might a designer choose Avalon for an FPGA project?

I believe it’s because it’s flexible and easy to configure?

Yes! Avalon offers different configurations to accommodate various design requirements, making it quite adaptable. Can anyone think of a scenario where such flexibility would be beneficial?

If we want to interface with various types of sensors or memory, that makes sense!

Precisely! Avalon allows you to cater to the unique needs of different components seamlessly.

Common Protocols - SPI, UART, I2C

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s explore some common communication protocols—SPI, UART, and I2C. Can anyone share what they know about these?

SPI is quite fast for short-distance communication, right?

Exactly! SPI is great for high-speed data transfer, especially between nearby devices. What about UART?

UART is used for serial communication and typically longer distances?

That's right! UART is relatively simple to implement, making it great for serial data transfers. And what about I2C?

I remember I2C allows multiple devices to communicate over just two wires.

Exactly! It's efficient and quite popular in connecting peripherals to microcontrollers. So, which protocol might you choose for a specific application? The right choice can enhance your design’s performance.

Conclusion of Interfaces

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

In summary, understanding these communication protocols—AXI, Avalon, SPI, UART, and I2C—is crucial for successful FPGA designs. Can anyone recap why these interfaces are essential?

Because they ensure different components can communicate efficiently, right?

Absolutely! They facilitate effective communication across subsystems, enabling you to build robust designs. Always consider the specific needs of your project when selecting an interface.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore various interface standards and communication protocols that facilitate communication between different subsystems in FPGA designs. It covers widely-used interfaces such as AXI, Avalon, SPI, UART, and I2C, emphasizing their roles in interconnecting IP cores and devices.

Detailed

Interface and Communication Protocols

System-level design often necessitates multiple subsystems that communicate effectively. FPGAs provide several interface standards to manage these interactions efficiently. Among the most significant are:

1. AXI (Advanced eXtensible Interface)

- Description: AXI is a high-performance interface designed for connecting various IP cores and subsystems within an FPGA. It supports high-bandwidth and low-latency communication, making it suitable for complex designs.

2. Avalon

- Description: The Avalon interface is a flexible bus system predominantly used in Intel FPGAs to interconnect IP cores. It allows for easy integration of different components while providing various configurations to suit different design needs.

3. Common Protocols**:

- SPI (Serial Peripheral Interface), UART (Universal Asynchronous Receiver/Transmitter), and I2C (Inter-Integrated Circuit) are standard communication protocols that enable seamless interaction between the FPGA and external devices, facilitating data transfer and device control.

Understanding these interfaces and protocols is essential for effective system-level design in FPGA applications, ensuring that various components can communicate as intended.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Interface Standards

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

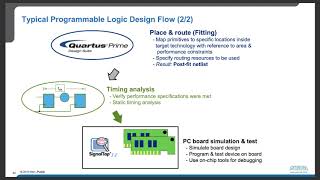

System-level design often involves multiple subsystems that need to communicate with each other. FPGAs provide various interface standards, such as:

Detailed Explanation

In modern FPGA design, it's essential to facilitate communication between different parts of the system. This is where interface standards come into play. These standards define how subsystems can effectively exchange data, ensuring that devices can connect and interact. By using these standardized protocols, designers can achieve interoperability between various IP cores and subsystems, simplifying the integration process.

Examples & Analogies

Think of interface standards as different languages spoken by people. Just as people need a common language to understand each other, subsystems in an FPGA system require standardized methods to communicate. If everyone speaks the same language, collaboration becomes much easier.

AXI Interface

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● AXI (Advanced eXtensible Interface): A high-performance, widely used interface for connecting different IP cores and subsystems.

Detailed Explanation

AXI, or Advanced eXtensible Interface, is a robust communication protocol that allows different IP blocks within an FPGA to communicate effectively. This interface is particularly popular due to its high performance, efficiency, and flexibility. AXI facilitates data transfers in a non-blocking manner, which means multiple transactions can occur simultaneously, enhancing the overall speed of the system. This makes AXI suitable for applications requiring fast data throughput, such as image processing or high-speed communications.

Examples & Analogies

Imagine a busy highway where many cars are moving in different directions without stopping. This is similar to how the AXI interface works, allowing multiple data transfers to occur simultaneously without waiting for one process to finish before starting another. This leads to efficient use of the 'road' (or data pathways) in the FPGA.

Avalon Interface

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Avalon: A flexible bus system used in Intel FPGAs for interconnecting IP cores.

Detailed Explanation

Avalon is another popular interface option, specifically tailored for use in Intel FPGA designs. Like AXI, it provides a means for different IP cores to communicate efficiently. The key feature of Avalon is its flexibility in handling various configurations, allowing designers to customize it according to the specific needs of their system. This adaptability makes it easier to connect different IP cores, especially when dealing with unique or customized modules.

Examples & Analogies

Think of the Avalon interface as a flexible bus system in a city, where buses can take multiple routes or adjust their schedules based on demand. Just as the bus system adapts to the needs of its passengers, Avalon allows connectivity between IP cores to be customized, ensuring the best fit for the design requirements.

Common Communication Protocols

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● SPI, UART, and I2C: Common protocols for communication between the FPGA and external devices.

Detailed Explanation

In addition to the broader interfaces like AXI and Avalon, there are specific communication protocols that facilitate interaction between the FPGA and external devices. SPI (Serial Peripheral Interface), UART (Universal Asynchronous Receiver/Transmitter), and I2C (Inter-Integrated Circuit) are widely used for their simplicity and effectiveness. Each of these protocols has unique characteristics and is suitable for different applications. For instance, SPI is often used for high-speed communication, while I2C is known for its simplicity in connecting multiple devices with minimal wiring.

Examples & Analogies

Imagine a group of friends communicating in a café. Some might prefer texting (UART), which allows private messages, while others use a group chat (I2C) to include everyone in a conversation without much fuss. Then, there are those who pass notes quickly (SPI) for fast exchanges. Each method is suitable for different social situations, just like these communication protocols serve varying needs in electronics.

Key Concepts

-

AXI: A high-performance interface that allows for efficient communication between FPGA components.

-

Avalon: A flexible interface standard used for reliable interconnections in Intel FPGAs.

-

SPI: A protocol enabling high-speed communication typically used for short distances.

-

UART: A simple, widely-used protocol for serial communication over longer distances.

-

I2C: A protocol that supports multiple devices with only two wires for communication.

Examples & Applications

Using AXI to connect a DSP core to a memory interface in a high-speed data processing application.

Employing UART for communication between an FPGA and a GPS module to retrieve location data.

Utilizing I2C to communicate with multiple sensors in a wearable health monitoring device, allowing simultaneous data collection.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In the world of FPGA and design, interfaces must be aligned. AXI, Avalon, in their prime, make communication sublime!

Stories

Imagine a team of builders (IP cores). Each builder communicates through a different lane: AXI on the fast lane, Avalon in a flexible route, while UART and I2C use their own paths, ensuring all work together!

Memory Tools

Remember SUI for communication protocols: S for SPI, U for UART, I for I2C.

Acronyms

AXI - Advanced eXtensible Interface; a speedy connector in your systems, providing efficiency and low latency.

Flash Cards

Glossary

- AXI

Advanced eXtensible Interface; a high-performance interface standard for connecting IP cores in FPGAs.

- Avalon

A flexible bus system used in Intel FPGAs for interconnecting IP cores.

- SPI

Serial Peripheral Interface; a synchronous serial communication protocol used for short-distance communication.

- UART

Universal Asynchronous Receiver/Transmitter; a hardware communication protocol for serial data transmission.

- I2C

Inter-Integrated Circuit; a multi-master, multi-slave, packet-switched, single-ended, serial communication bus.

Reference links

Supplementary resources to enhance your learning experience.