Connecting IP Cores

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Connecting IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to learn about the crucial step of connecting IP cores in our FPGA designs. Does anyone know what might happen if we don’t connect them properly?

Maybe the data won't flow correctly between them?

Or they might not function at all!

Exactly! Proper connections ensure that data and control signals flow smoothly between the cores. We'll discuss how we can achieve that. The first aspect we'll look at is the use of a system bus. Can anyone tell me what a system bus is?

Does it act like a highway for data?

Great analogy! Yes, a system bus facilitates communication between different IP cores, like Avalon or AXI buses. Understanding this will help us visualize how to manage our connections effectively.

What types of signals do we need to connect?

Good question! We also need to ensure that control signals are routed correctly. These signals are essential for timing and operation, as they control when and how data is processed.

To summarize, connecting IP cores involves using system buses for data transfer and synchronizing control signals. Any thoughts on why this synchronization might be important?

It must ensure all parts work together at the right time.

Exactly right! Ensuring synchronization keeps the entire system running smoothly. Let’s move on to practical examples next.

Practical Implementation of Connections

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive deeper into our bus options. Student_3, can you tell us what the AXI bus is used for?

Isn't AXI a high-performance interface for connecting IP cores?

Correct! Its high bandwidth makes it suitable for demanding applications. What about Avalon? What makes it special?

Avalon is more flexible and suited for Intel FPGAs, right?

Yes! It’s tailored for better integration in Intel architectures, enhancing connectivity with various functions. Let’s summarize what we have learned so far about connections.

Today, we've covered the importance of using system buses like AXI and Avalon for connecting IP cores and ensuring that our control signals are synchronized. Why do you think flexibility in buses could be advantageous?

Flexibility allows us to tailor systems to different needs.

Absolutely! That flexibility will help us adapt designs for various applications. Excellent participation, everyone!

Control Signals and Their Importance

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we've connected the dots with buses, let’s talk about control signals. Student_2, can you explain why control signals are crucial?

They ensure that different parts of the system work in harmony.

Exactly! Without proper synchronization of control signals, we might encounter timing issues, leading to errors. Can anyone give me examples of control signals we need?

Reset signals and clock signals come to mind.

Perfect! The reset signal initializes the state, while the clock signal dictates operation timing. Let’s think about how this applies in a project with both UART and FIFO cores.

How do we ensure they read/write at the right times?

Great question! By carefully mapping out control signals and making sure they are in sync with both the operating clock and functional requirements. Always double-check your connections!

In conclusion, establishing the right control signals enhances overall performance. Why is testing those connections essential, everyone?

To ensure everything works as expected before deploying?

Exactly! Thorough testing allows us to catch issues early on. Excellent work today, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

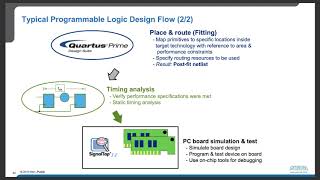

In connecting IP cores, designers create interconnections between various cores to form a complete system while ensuring proper data flow, control signals, and synchronization. Key components such as system buses (like Avalon or AXI) are crucial for managing these connections.

Detailed

Detailed Summary

In FPGA designs, connecting IP cores effectively is critical for achieving a functional and efficient system. After the configuration of each IP core, the next step involves establishing the necessary connections to integrate them into a cohesive unit. This section outlines several significant points:

Key Components in Connecting IP Cores

- System Bus: To facilitate the interconnection of multiple IP cores, designers typically utilize a system bus such as Avalon or AXI. These buses serve as communication channels that manage data transfers between cores.

- Control Signals: Proper routing and synchronization of control signals for each IP core are essential. Designers must ensure that these signals align with the system's timing requirements to maintain operational integrity.

By understanding how to connect IP cores using system buses and control signals, designers can create efficient designs that meet specified functionalities.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Creating Interconnections Between Cores

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

After configuring the cores, the next step is to connect them to form the complete system. This involves creating the interconnections between various cores and ensuring that data flows correctly between them.

Detailed Explanation

Once you have set up the individual IP cores and adjusted their configurations, the next step is to connect these cores to create a functional system. Connecting involves laying out a proper communication pathway between the cores so they can exchange data. For instance, if one core produces data, another core might need to consume that data, and this exchange needs to happen smoothly. The design tools you use will help create these interconnections visually, often through a graphical interface.

Examples & Analogies

Think of this step like connecting various devices in a smart home. If you have a smart thermostat, smart lights, and a security camera, you need to ensure they're all connected to a central hub to communicate. Just like smart devices need the right wires or wireless connections to function together, IP cores need to be connected effectively for the entire FPGA system to work.

Using a System Bus

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Use a system bus (e.g., Avalon, AXI) to connect IP cores and manage data transfers.

Detailed Explanation

'A system bus is like a central highway that connects all the components (or cores) of your FPGA design. When IP cores need to send or receive data, they send it over this bus. The bus handles multiple connections simultaneously, allowing each core to function efficiently without stepping on each other’s toes. By using a recognized protocol like Avalon or AXI, you ensure that the data format and timing are consistent, which helps minimize errors and streamlines communication.

Examples & Analogies

Imagine a busy highway where different vehicles (cars, trucks, buses) travel. The highway allows these vehicles to reach their destination without collisions, as there are rules (traffic signals, lanes) to follow. In the context of IP cores, the system bus acts like that highway, ensuring smooth communication between various components while following established protocols.

Routing Control Signals

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Ensure that the control signals for each IP core are correctly routed and synchronized with the system’s timing.

Detailed Explanation

In addition to data signals, control signals are crucial for the proper functioning of IP cores. These signals dictate when to read or write data, reset the core, or change operation modes. Correctly routing these signals involves defining how they will travel through the system to ensure they reach the appropriate cores at the right time. Synchronizing these signals is also vital; this means making sure that timing of the control signals aligns with the clock signals used in the design. Without proper synchronization, the cores may operate out of phase, leading to errors and unpredictable behavior.

Examples & Analogies

Consider a conductor leading an orchestra. The conductor signals when musicians should play their parts—if they don’t follow the conductor’s direction, the performance will be chaotic. In FPGA design, control signals serve this orchestral role by ensuring that each IP core plays its 'note' at the right time, maintaining harmony in the system.

Key Concepts

-

System Bus: A communications pathway connecting IP cores for data transfer.

-

Control Signals: Synchronization signals essential for proper operations among cores.

-

AXI: A high-performance interface for efficient integration of FPGA components.

-

Avalon: A flexible bus system specifically for Intel FPGA designs.

Examples & Applications

In a UART-FIFO integration, using a system bus like AXI allows seamless data flow between the core handling serial communication (UART) and the one managing data buffers (FIFO).

Using control signals such as reset and clock ensures both the UART and FIFO cores operate in sync, preventing data loss during transfers.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

A bus goes zoom, connecting by room; control signals in time, keep all in line.

Stories

Imagine each IP core as a friend at a party; the system bus is the main hallway where they all interact, and control signals like the DJ ensure everyone dances to the same beat.

Memory Tools

BAND: Bus And Networking Devices (to remember the role of a bus).

Acronyms

BCS

Bus Connecting System (to denote the importance of buses in FPGA design).

Flash Cards

Glossary

- System Bus

A communication pathway that connects different IP cores in an FPGA, facilitating data transfer.

- Control Signals

Signals that synchronize operations among IP cores and ensure orderly processing of data.

- AXI

Advanced eXtensible Interface, a high-performance bus commonly used in FPGA designs for connecting components.

- Avalon

A flexible bus system utilized typically in Intel FPGAs for integrating IP cores.

Reference links

Supplementary resources to enhance your learning experience.