Integration of IP Cores into FPGA Designs

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Selecting the Right IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will begin by discussing how to choose the right IP cores for your FPGA designs. Can anyone tell me what we need to consider when selecting an IP core?

Is it about what kind of functionality we want the design to have?

Exactly! Identifying the specific functionality required, like communication protocols or processing power, is crucial. This ensures that the IP core can meet our design goals. We also have to think about performance and resource usage.

What do you mean by performance and resource usage?

Good question! Performance refers to how fast and efficient the IP core is, while resource usage indicates how many FPGA resources it consumes. Balancing these factors is key. Remember the acronym 'PR' for Performance and Resources!

So must we choose high performance cores always?

Not necessarily. Sometimes a balance of flexibility and efficiency is more valuable. It's about matching the IP core's characteristics with your project needs.

What if we choose a core that uses too many resources?

Then, it could lead to an inefficient design. Evaluating how selected IP cores impact overall resource usage helps avoid this issue. Let's summarize: Choose cores that fit both the functionality and resource constraints of your design.

Configuring IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s talk about the configuration of the chosen IP cores. Why do you think configuration is vital for successful integration?

Is it because every project has different requirements?

Absolutely! Each core comes with parameters that can be tuned, such as data width or clock frequency. Configuring them to fit your design is essential. Can anyone name one of these parameters?

Data width?

Correct! Besides data width, you must also synchronize clock and reset signals. Remember to configure these so they align with your system requirements. A helpful mnemonic is 'TIM' for Timing, Interface, and Mapping!

How does the interface mapping work?

Good point! Interface mapping is linking the inputs and outputs of your IP cores to the signals in your design. It ensures data flows correctly. Let's summarize: Proper configuration involves tuning core parameters, synchronization, and careful interface mapping.

Connecting IP Cores

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we have configured the IP cores, what do you think is the next step?

Connecting them together?

Exactly! Connecting these cores is essential to form the complete system. What are the different ways we can connect them?

We could use a system bus?

Right! A system bus like AXI or Avalon can connect the cores and manage data transfers. It's important to ensure that control signals are routed correctly as well. Can anybody think of what control signals are critical?

Like reset and clock signals?

Exactly! Remembering to sync these control signals prevents timing issues. We can also use the acronym 'C2S', which stands for Control to Signals!

What happens if we don’t connect them properly?

If not correctly connected, data transmission issues can occur. In summary, ensure you connect the cores using a bus and synchronize control signals to facilitate a functional design.

Example: Integration of UART and FIFO

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s finish by walking through a practical example of integrating the UART and FIFO IP cores. What does the UART core do?

It handles serial communication.

Correct! And the FIFO is used for buffering data. The first step is to select the cores. What configurations might we change for the UART?

We might set the data width and baud rate.

Exactly! Then we’ll map the UART TX and RX pins to the FIFO's inputs and outputs to ensure proper flow. What’s next after configuration?

Connecting control signals?

Yes! Connecting control signals like reset and clock is crucial. Finally, we should simulate the system. Why is simulation important?

To check if everything works as expected?

Exactly! Simulating helps validate the integration and ensures data transmission is working properly. Remember, the sequence is select, configure, connect, and simulate. Well done in this session!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The integration of IP cores into FPGA systems involves three main steps: selecting appropriate IP cores based on design requirements, configuring them using FPGA tools, and connecting the configured cores to facilitate communication within the design. The section further illustrates this process with an example of integrating a UART and a FIFO IP core.

Detailed

Detailed Summary

The integration of IP cores into FPGA designs is a vital process for creating complex and efficient systems. This process consists of several key steps:

Selecting the Right IP Cores

- Design Requirements: Understand the specific needs of the project, such as desired functionality and performance aspects. This includes determining which communication protocols and the necessary processing power are required to meet system objectives.

- Performance Considerations: Balance the speed and efficiency of chosen cores against flexibility. Some cores provide high performance but limited customization, whereas others might be more adaptable at the cost of speed.

- Resource Utilization: Analyze how the chosen cores will consume FPGA resources like logic blocks, memory, and I/O pins, ensuring that the overall design remains within limits.

Configuring IP Cores

Once the correct cores are identified, configuration is the next important step.

- Configuration Parameters: Modify settings like data width, clock frequencies, and protocol specifications based on the project's requirements.

- Clocking and Reset: Ensure synchronization with the system’s clock and reset signals to maintain coherent operations.

- Interface Mapping: Accurately map the IP core inputs and outputs to corresponding signals within the system.

Connecting IP Cores

After configuring the cores, the next phase involves establishing interconnections for effective data transfer.

- System Bus: High-performance bus systems like AXI or Avalon can facilitate robust communication among cores.

- Control Signals: Correct routing and synchronization of control signals are crucial for efficient timing coordination across the design.

Example: Integration of UART and FIFO IP Cores

An example highlights the steps taken to integrate UART, responsible for serial communication, with a FIFO buffer for data buffering:

1. Core Selection: Utilize configuration tools to set parameters like UART data width and FIFO buffer size.

2. Interface Configuration: Map UART TX/RX to FIFO inputs/outputs, ensuring optimal data flow.

3. Control Signal Connections: Properly align control signals with system logic.

4. Simulation: Validate interactions with a testbench to ensure data integrity and operational reliability.

In summary, seamless integration of IP cores enhances the design process, allowing developers to build performant, scalable FPGA systems that effectively meet specified requirements.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of Integration Steps

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The integration of IP cores into FPGA designs involves several steps, including selecting the appropriate IP cores, configuring them, and ensuring that they work together seamlessly in the design.

Detailed Explanation

Integrating IP cores into an FPGA design is a multi-step process that begins with selecting the right cores for your project. It's crucial to pick cores that match the specific functionalities your design requires. After selection, you'll configure these cores so they perform correctly within the overall system. Lastly, you'll ensure that all the cores function together harmoniously, allowing data to flow smoothly between them.

Examples & Analogies

Think of it like assembling a team for a project. First, you gather members with the right skills (selecting IP cores), then you discuss and agree on roles (configuring cores), and finally, you ensure everyone knows how to collaborate effectively (ensuring seamless operation).

Selecting the Right IP Cores

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Design Requirements: Identify the specific functionality required for the system, such as communication protocols or processing power. Select IP cores that best meet these needs.

● Performance Considerations: Some IP cores are optimized for speed and efficiency, while others offer flexibility at the cost of performance. Make sure to balance performance requirements with resource constraints.

● Resource Utilization: IP cores use various FPGA resources like logic blocks, memory, and I/O pins. Evaluate how the selected IP cores impact overall resource usage.

Detailed Explanation

Choosing the right IP core is fundamental to your design. You start by assessing what functions you need—like specific communication techniques or necessary processing capacity. Next, you should consider how each core performs; some might be faster but less adaptable, while others might be versatile but slower. You also need to check how much of the FPGA’s resources each core will use, ensuring you have sufficient capacity for everything your design requires.

Examples & Analogies

This is similar to picking ingredients for a recipe. You need to know what dish you want to prepare (design requirements), choose the freshest or most suitable ingredients (performance considerations), and make sure you have enough space in your kitchen (resource utilization) to cook everything efficiently.

Configuring IP Cores

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

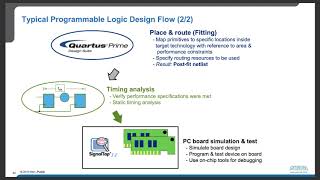

Once the IP cores are selected, they need to be configured to fit the design’s requirements. FPGA design tools such as Vivado (Xilinx) or Quartus (Intel) typically provide IP core configuration wizards that allow designers to customize the settings of the IP cores.

● Configuration Parameters: IP cores often have customizable parameters, such as data width, clock frequency, buffer sizes, and protocol settings.

● Clocking and Reset: Ensure that the IP cores are correctly synchronized with the system’s clock and reset signals.

● Interface Mapping: Map the inputs and outputs of the IP cores to the appropriate signals in the system.

Detailed Explanation

After selecting the IP cores, the next critical step is to configure them. This process involves adjusting settings tailored to your project's requirements. Each IP core has specific parameters you can customize, such as its data handling capacity or speed. You also need to make sure the timing signals are correctly managed and that inputs and outputs are properly linked to the rest of the system for coherent operation.

Examples & Analogies

Imagine you just bought a new smartphone. You need to set it up by choosing your language, installing apps, and syncing it with other devices (configuring IP cores). Just like you would need a Wi-Fi connection to go online, the cores must be properly connected and timed to communicate effectively with one another.

Connecting IP Cores

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

After configuring the cores, the next step is to connect them to form the complete system. This involves creating the interconnections between various cores and ensuring that data flows correctly between them.

● System Bus: Use a system bus (e.g., Avalon, AXI) to connect IP cores and manage data transfers.

● Control Signals: Ensure that the control signals for each IP core are correctly routed and synchronized with the system’s timing.

Detailed Explanation

Connecting the configured IP cores is essential to creating a functional system. You establish links between the cores so they can exchange data effectively. This is often facilitated by a 'system bus,' which serves as a communication pathway. Additionally, control signals—essential instructions that dictate how and when cores act—must be properly aligned to coordinate their operations across the system.

Examples & Analogies

Think of it like setting up a network of friends for a group project. Each friend has a specific role (IP core), and you need to ensure they are all in communication and working together (connecting and routing signals) so the project runs smoothly and efficiently.

Example: Integration of UART and FIFO IP Cores

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Here’s an example of integrating two commonly used IP cores—UART and FIFO (First In, First Out) buffer—into an FPGA design. The UART core is responsible for serial communication, and the FIFO core is used to buffer data between the UART and a processing system.

1. Select UART and FIFO IP Cores: Use the configuration wizard in the FPGA tool to select and configure the UART and FIFO cores. Set the UART data width, baud rate, and FIFO buffer size.

2. Configure Interfaces: Map the UART TX and RX pins to the FIFO input and output respectively, ensuring proper data flow.

3. Connect Control Signals: Connect the control signals like reset, clock, and FIFO write/read enable to the appropriate logic in the system.

4. Simulate the System: Use a testbench to simulate the interaction between the UART and FIFO, checking for correct data transmission and buffer management.

Detailed Explanation

To illustrate the integration process, let’s consider the UART core, responsible for serial data transmission, and the FIFO buffer, which temporarily stores data. The steps include selecting and configuring both cores based on the design's needs, mapping the connections for data flow, coordinating control signals to manage operations between the two cores effectively, and finally simulating the entire setup to ensure they work together as intended.

Examples & Analogies

Imagine you're coordinating a relaying system at a race track where one team passes a baton to the next (UART sending data). The FIFO acts like a waiting area where the baton is held until the next runner is ready to go (FIFO buffering). You need to ensure the distance between lanes (mapping interfaces) is clear so the transition is smooth and typically practice that transition before the actual race to ensure it's timed perfectly (simulation).

Key Concepts

-

Integration Process: The series of steps for effectively combining IP cores into FPGA designs.

-

Selection Criteria: Factors like functionality and performance that influence the choice of IP cores.

-

Configuration Steps: The methods of modifying core parameters to meet design needs.

-

Connection Methods: Techniques for interconnecting the configured IP cores to create a cohesive system.

Examples & Applications

An example of integrating a UART core with a FIFO buffer demonstrates how to set data width and baud rate and connect signal lines to ensure proper communication.

Selecting a memory controller IP core and configuring it for specific memory types like SDRAM requires understanding the system's resource utilization.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When choosing cores, remember PR, choose the best for the job, don't stray far!

Stories

Imagine building a bridge with blocks (IP cores), each needs to fit together just right to connect on both sides (connecting).

Memory Tools

For configuration, think 'CTP': Clock, Timing, Parameters.

Acronyms

Use 'SBC' for connection

System Bus

connections

Control signals.

Flash Cards

Glossary

- IP Core

Pre-designed, reusable logic modules that implement specific functions within an FPGA.

- Hard IP Cores

Fixed hardware blocks implemented directly in silicon, offering high performance.

- Soft IP Cores

Cores described using Hardware Description Languages and synthesized into an FPGA's fabric, providing flexibility.

- System Bus

A communication pathway in FPGA designs connecting different IP cores for data transfer.

- Configuration Parameters

Settings that can be modified in an IP core, such as clock frequency and data width.

- Clock Domain

A section of an FPGA that operates under a specific clock signal.

- Simulation

Testing the design through software to ensure functionality before hardware implementation.

Reference links

Supplementary resources to enhance your learning experience.