Configuring IP Cores

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Configuration Parameters

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll explore the critical configuration parameters for IP cores. Can anyone tell me what some of these parameters might include?

Is data width one of the parameters?

Exactly, Student_1! Data width is one key parameter. It defines how much data the core can process simultaneously, impacting both performance and efficiency. What about other parameters?

What about clock frequency?

Correct! Clock frequency determines the operational speed of the IP core. Higher frequencies can lead to better performance but also might increase power consumption. Also, the resources need to be matched accordingly.

And what about buffer sizes?

Great point, Student_3! Buffer sizes are crucial for data handling and can affect throughput significantly. It's all about balancing these parameters effectively.

So to recap: the key configuration parameters are data width, clock frequency, and buffer sizes, which all influence core performance.

Synchronization of Clock and Reset Signals

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let's discuss synchronization. Why is it essential for IP cores?

If they're not synchronized, it could lead to timing issues, right?

Absolutely, Student_4! When IP cores are out of sync with the system clock or reset signals, it can cause data corruption or functionality failures. What happens if we don't synchronize correctly?

The system might not function as expected or could even crash.

Exactly! Ensuring synchronization helps maintain data integrity and system reliability. Always double-check that all cores are synchronized to the appropriate signals.

In summary, proper synchronization of clock and reset signals is vital for the IP core's performance and functioning.

Interface Mapping

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's address interface mapping. How does this contribute to the overall FPGA design?

It allows the IP cores to communicate effectively with each other and with external components.

Exactly, Student_2! Proper interface mapping ensures smooth data flow, which is essential for maintaining efficiency in an integrated system. Can someone explain what might happen if the mappings are incorrect?

Data could get lost or mixed up, which can lead to incorrect outputs.

Correct! Misconfigured mappings can severely hinder application performance. Always validate your interface mappings during the design phase.

To sum up, correct interface mapping ensures that IP cores connect and communicate properly, safeguarding data integrity within the system.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The process of configuring IP cores includes selecting appropriate configuration parameters, ensuring proper synchronization with clock and reset signals, and mapping interfaces correctly. Different configuration steps help achieve optimal performance and correct functionality in the integrated FPGA design.

Detailed

Configuring IP Cores

Configuring IP cores is a critical process in FPGA design, where selected IP cores must be adjusted to align with the specific requirements of the project. This section outlines key aspects of this process, which involves several steps:

Configuration Parameters

IP cores often have customizable settings that impact their function and performance. Examples of these parameters include:

- Data Width: Determines how much data can be processed at a time, affecting bandwidth and performance.

- Clock Frequency: Sets the operational speed of the IP core, influencing the timing and overall system performance.

- Buffer Sizes: Impacts how data is stored temporarily, which can affect throughput.

- Protocol Settings: Needed for communication-enabled cores, for example, UART or I2C modulations.

Clocking and Reset

One must ensure that the IP cores are appropriately synchronized with the system's clock and reset signals. This synchronization is essential for avoiding timing issues and ensuring efficient operation.

Interface Mapping

This involves connecting the inputs and outputs of the IP cores to corresponding signals in the design. Correct mapping is critical to ensure data flows appropriately between cores and other system components.

In summary, proper configuration of IP cores is vital to the success of an FPGA design, as it enables customization that meets specific application requirements while maximizing performance.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Configuration

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

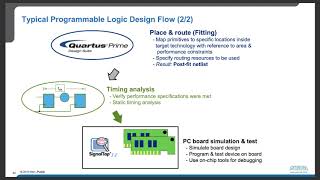

Once the IP cores are selected, they need to be configured to fit the design’s requirements. FPGA design tools such as Vivado (Xilinx) or Quartus (Intel) typically provide IP core configuration wizards that allow designers to customize the settings of the IP cores.

Detailed Explanation

After choosing appropriate IP cores for your FPGA design, the next step is to configure them. Configuration means setting parameters so that each IP core works effectively within the design requirements. Popular FPGA design tools like Vivado or Quartus assist this process by offering configuration wizards. These tools guide designers through various options to adjust settings for compatibility with their specific design.

Examples & Analogies

Think of this process like customizing a car after buying it. When you choose a car model, you then select features like color, wheels, and interior styles that suit your preference. Similarly, configuring IP cores involves setting options that optimize their performance in your FPGA design.

Configuration Parameters

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Configuration Parameters: IP cores often have customizable parameters, such as data width, clock frequency, buffer sizes, and protocol settings.

Detailed Explanation

Each IP core has specific settings known as configuration parameters. These can be adjusted according to the project's needs. For example, the 'data width' setting determines how much data can be processed at once—wider data paths can handle more information but might use more resources. The 'clock frequency' controls how quickly the core operates, proposing a balance between speed and power consumption. Other parameters, like 'buffer sizes' and 'protocol settings,' ensure that the IP cores fit together smoothly in the design.

Examples & Analogies

Imagine you're organizing a team for a project. Each member has specific strengths (data width) and can work at different speeds (clock frequency). To make the team more effective, you need to assign them tasks that match their strengths and how quickly they can work. In the same way, configuring IP cores helps ensure that each component of your design is well-suited to its role.

Clocking and Reset

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Clocking and Reset: Ensure that the IP cores are correctly synchronized with the system’s clock and reset signals.

Detailed Explanation

To function correctly, IP cores must be synchronized with the overall system clock. This means they should receive the same timing signals to ensure data flows correctly and avoids errors. Additionally, every system needs a reset signal to initialize components when the system starts or in case of an error. Properly managing these clock and reset signals is crucial for ensuring that all parts of the design operate reliably.

Examples & Analogies

Imagine a choir performing a song. Each singer must follow the conductor's cues (the clock) to stay in harmony. If one singer starts too early or late, it may lead to a confusing performance. The reset signal is akin to the conductor asking everyone to start over if things go wrong. Similarly, in an FPGA design, synchronized clocking and correct reset signals ensure that all IP cores work together in harmony.

Interface Mapping

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Interface Mapping: Map the inputs and outputs of the IP cores to the appropriate signals in the system.

Detailed Explanation

After configuration, the next step involves mapping. This process entails connecting the inputs and outputs of the IP cores with the rest of the system's signals. It ensures that data flows seamlessly between different components. For example, the output of one core might need to connect to the input of another core, creating a chain of communication. Proper mapping guarantees that each part of the system can exchange information effectively.

Examples & Analogies

Consider a team of workers on a construction site. Each worker needs to pass materials (input/output signals) to the right person (other components) to keep the project moving forward. Interface mapping in FPGA is similar—ensuring that each core is connected to the correct signals is essential for the entire design to function properly, just like ensuring the right materials get to the right workers.

Key Concepts

-

Configuration Parameters: These include customizable settings such as data width, clock frequency, and buffer sizes that directly affect IP core performance.

-

Clocking and Reset Signals: Proper synchronization of these signals is crucial for ensuring consistency and functionality of IP cores.

-

Interface Mapping: This process ensures that data flows correctly between various cores, which is vital for system integration.

Examples & Applications

Configuring a UART IP core involves specifying the data width and baud rate to ensure proper serial communication.

For a FIFO buffer, a designer would set the buffer size and ensure correct mapping to the sender and receiver components.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Data width wide, clock signals tied, map interfaces right, for a system that's bright.

Stories

Imagine an orchestra where each musician (IP core) must start at the same time (synchronized clock) and play their part accurately (configured parameters) to create a beautiful symphony (effective system).

Memory Tools

D.C.I. - Data width, Clock signal, Interface mapping.

Acronyms

C.W.I. - Configuration, Synchronization, Mapping.

Flash Cards

Glossary

- Configuration Parameters

Customizable settings for an IP core, including data width, clock frequency, buffer sizes, and protocol settings.

- Clock Signal

A timing signal used to synchronize operations in digital circuits.

- Interface Mapping

The process of connecting the inputs and outputs of the IP cores to the corresponding signals in the overall design.

Reference links

Supplementary resources to enhance your learning experience.