System-Level Design Concepts

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Modular Design Approach

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're diving into modular design in system-level FPGA design. Can anyone explain what a top-level module is?

Isn’t it the main module that connects all other modules together?

Exactly, great point! The top-level module acts as the orchestrator of various sub-modules. Why do you think it's beneficial to break down the design into smaller modules?

Maybe it’s easier to manage and debug smaller parts?

Absolutely! Smaller modules enhance maintainability. Plus, you can reuse IP cores in different designs. This is sometimes referred to as 'modularity makes for maintainability'.

So, we can work on different modules simultaneously, right?

Exactly! That leads to faster development. Can anyone give examples of how IP core reusability can save time?

If we use a standard UART core, it saves us the effort of designing serial communication from scratch!

Great example! In summary, modular design helps simplify the process and supports reusability, which is crucial for efficient FPGA development.

Interface and Communication Protocols

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's move on to communication protocols. Who can name some common protocols used with FPGAs?

I know SPI and I2C are popular for communication.

That's correct! They allow for various devices to communicate with the FPGA. What about AXI—what is it used for?

AXI is a high-performance interface used to connect different IP cores.

Exactly! The AXI interface is essential for high-speed data transfers. Why do you think having different communication protocols is important?

So that we can interface with various devices and utilize their unique functionalities?

Correct! The diversity of protocols ensures versatility in system design. Can anyone share another example of a communication need?

If we need to connect sensors to an FPGA, we’d likely use I2C.

Great example! In summary, implementing multiple communication protocols allows us to enhance the FPGA's capabilities for different applications.

Timing Constraints and Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s discuss timing constraints. Why is timing so critical in FPGA systems?

Because all parts need to work together without delays, right?

Exactly! Timing violations can cause malfunctioning systems. What is one method we can use to manage timing across different clock domains?

We can use clock domain crossing techniques.

Correct! Techniques like FIFOs can help manage data transfer between asynchronous clock domains. Can anyone explain how timing analysis is performed?

We would use FPGA design tools to perform static timing analysis.

Right again! Timing analysis tools identify potential violations. Let’s wrap up—why is resource allocation important?

It helps minimize delays and the critical path, keeping everything synchronized.

Exactly! Efficient resource allocation directly impacts the FPGA’s performance. Excellent work, everyone!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In system-level design, components like IP cores and custom logic are amalgamated to create a coherent FPGA system. This approach entails modular design, multiple communication protocols, and meticulous management of timing constraints to ensure efficient and synchronized operation.

Detailed

Detailed Summary

System-level design concepts focus on crafting comprehensive FPGA-based systems that seamlessly incorporate various components such as IP cores, custom logic, memory, and communication interfaces. This integrative process entails careful planning and management of resources to optimize performance. The key aspects of system-level design include:

1. Modular Design Approach

- Top-Level Module: This is the main design entity that integrates all sub-modules, allowing easy organization of the system.

- Sub-modules: Smaller, reusable modules that encapsulate specific functionality, enhancing maintainability and debugging.

- IP Core Reusability: Encouraging the use of standard IP cores to minimize development time across different designs.

2. Interface and Communication Protocols

System-level design often necessitates multiple subsystems communicating effectively, with various interface standards available:

- AXI: High-performance interface connecting different IP cores.

- Avalon: Flexible bus for Intel FPGAs.

- Common Protocols: SPI, UART, and I2C for communication with external devices.

3. Timing Constraints and Optimization

Ensuring synchronous function across components is critical, which involves:

- Clock Domain Crossing: Managing transfers between different clock domains.

- Timing Analysis: Utilizing timing analysis tools to identify and resolve potential violations.

- Resource Allocation: Optimizing IP core and logic placements to minimize signal delays.

This section reinforces the significance of structured system-level design in developing high-performance FPGA systems that meet specific requirements through effective integration.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of System-Level Design

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

System-level design involves the creation of a complete FPGA-based system that integrates multiple components, including IP cores, custom logic, memory, and interfaces. It requires careful planning, resource management, and performance optimization.

Detailed Explanation

System-level design refers to the process of designing an entire system within an FPGA, not just isolated components. This approach means thinking about how different parts of the system work together. Designers must consider how to manage resources effectively (like the FPGA's logic elements, memory, and I/O) and ensure that the system works efficiently in terms of performance.

Examples & Analogies

Think of building a house—not just constructing walls but designing the whole structure, including plumbing, electricity, and layouts for different rooms. You must plan how everything connects to work harmoniously, just like how an FPGA designer must integrate multiple IP cores and components.

Modular Design Approach

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Modular Design Approach

- Top-Level Module: The top-level module is the highest-level design entity that connects all the sub-modules, including IP cores, custom logic, and memory elements.

- Sub-modules: Break the design into smaller, reusable modules, each responsible for a specific functionality. This modular approach simplifies the design process, improves maintainability, and facilitates debugging.

- IP Core Reusability: Use standard IP cores across different designs to ensure reusability and reduce development time.

Detailed Explanation

The modular design approach is about breaking a large project into smaller, manageable sections, known as modules. Each module serves a unique purpose, making it easier to design, test, and modify. The top-level module acts as a 'brain,' connecting all these modules together. Additionally, using existing IP cores in various projects saves time and ensures reliability, as these cores are proven solutions.

Examples & Analogies

Imagine cooking a multi-course meal, where each dish is made separately but contributes to the full dining experience. You wouldn't mix everything in one pot; instead, you prepare each dish according to its recipe. This keeps things organized and allows any dish to be re-used in future meals.

Interface and Communication Protocols

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Interface and Communication Protocols

System-level design often involves multiple subsystems that need to communicate with each other. FPGAs provide various interface standards, such as:

- AXI (Advanced eXtensible Interface): A high-performance, widely used interface for connecting different IP cores and subsystems.

- Avalon: A flexible bus system used in Intel FPGAs for interconnecting IP cores.

- SPI, UART, and I2C: Common protocols for communication between the FPGA and external devices.

Detailed Explanation

In system-level design, different parts of the FPGA system need to share information effectively. This is where interfaces and communication protocols come into play. AXI and Avalon provide structured ways for components to talk to each other, while protocols like SPI, UART, and I2C allow the FPGA to communicate with devices outside the FPGA, like sensors or controllers.

Examples & Analogies

Consider a telephone network where different callers (subsystems) use different protocols (communication methods) to convey messages. Just as every caller must understand how the network operates to communicate effectively, FPGAs use standardized interfaces to ensure all components understand each other.

Timing Constraints and Optimization

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

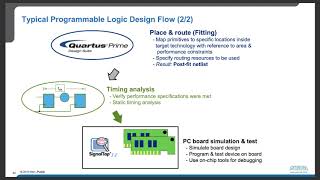

Timing Constraints and Optimization

When designing complex systems, it’s crucial to consider timing constraints to ensure that all components function synchronously. This involves:

- Clock Domain Crossing: Managing data transfers between different clock domains (e.g., different frequencies or asynchronous signals).

- Timing Analysis: Use FPGA design tools to perform static timing analysis and identify potential timing violations.

- Resource Allocation: Optimize the placement of IP cores and custom logic to minimize signal propagation delays and reduce critical path lengths.

Detailed Explanation

Timing constraints ensure that all parts of the FPGA system operate at the same speed and can communicate effectively without errors. Clock domain crossing is particularly challenging, as it involves handling signals that may operate on different timing schedules. Designers must analyze the timing of their designs to catch any issues before they arise, tweaking the layout and connections to enhance performance.

Examples & Analogies

Think of running a relay race. Each runner (component) must pass the baton (data) precisely at the right time; otherwise, the team loses speed. Timing analysis is akin to training the runners to ensure they know when and how to pass the baton, minimizing delays on the track.

Key Concepts

-

Modular Design: The systematic division of a design into smaller, reusable units.

-

Communication Protocols: Standards governing data transmission between components.

-

Timing Constraints: Restrictions ensuring components operate within synchronized timeframes.

-

Clock Domain Crossing: Managing data transfers between multiple clock frequencies.

Examples & Applications

Using a UART to enable serial communication with external devices in an FPGA design.

Utilizing the AXI protocol to connect high-speed peripherals in a complex FPGA system.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Modular design, small but mighty, keeps our systems neat and tidy!

Stories

Imagine building a toy castle from blocks where each block can fit together in different ways—a modular design allows for endless creations and easy fixes!

Memory Tools

Use 'MATRIX' to remember important factors in scheduling: Modularity, Accurate communication, Timing constraints, Resource management, Interfaces, and X-factor improvements.

Acronyms

Remember 'ACCRON' for optimal design

**A**llocate resources

**C**ommunicate well

**C**onduct timing analysis

**R**euse components

**O**ptimize performance

**N**avigate protocols.

Flash Cards

Glossary

- Modular Design

An approach that divides a system into smaller, manageable, and reusable modules.

- TopLevel Module

The primary module in a design that integrates and connects all sub-modules.

- Submodules

Smaller design units within the top-level module that perform specific functions.

- Communication Protocols

Agreements that define the rules for data exchange between hardware components.

- AXI

Advanced eXtensible Interface, a high-performance interface standard for connecting IP cores.

- Clock Domain Crossing

The process of transferring data between different clock domains with varying frequencies.

- Timing Analysis

The examination of a design to ensure that all timing requirements are met to avoid violations.

Reference links

Supplementary resources to enhance your learning experience.