Challenges During Tape-Out

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Final Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start our discussion about the tape-out process. One of the main challenges is final verification. Can anyone explain what we mean by final verification in this context?

I think it's when we check to make sure that there are no errors left after we've done all our optimizations, right?

Exactly! Final verification is crucial because even small errors that were missed earlier can have significant consequences. This is why thorough checks are essential. A good way to remember this is the phrase 'Check to Protect'—we check our work to protect against errors.

What kinds of errors should we be looking for during this final check?

Great question! We look for design rule violations, connectivity issues, and any violations of electrical rules. Think of it as a last resort to ensure everything aligns before fabrication. Can anyone think of examples of such violations?

Maybe something like an incorrect connection between transistors?

Yes, exactly! That could lead to significant functional issues later on. To summarize this key point: Final verification is about ensuring no overlooked errors remain through rigorous assessment, which directly impacts the success of the tape-out!

Last-Minute Design Changes

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s delve into another challenge: last-minute design changes. Who can explain why these changes might occur so late in the tape-out process?

I guess sometimes there are new requirements or issues that come up that need to be addressed quickly.

Exactly! New requirements can arise from stakeholders or last-minute discoveries during verification. These changes can create a whirlwind of rework. A fun way to remember this is with 'Change is the Only Constant'—just like in life, design often requires last-minute adjustments.

So, what can we do to manage these last-minute changes?

Good question, Student_1! Effective communication within the design team is key, along with flexibility in design processes to accommodate changes. Would anyone like to share an experience where last-minute changes caused issues?

Last semester, our project faced delays because we missed a requested feature that came in late.

That’s a perfect example! It reinforces the idea of proactive collaboration. In summary, last-minute changes are common, but managing them effectively is crucial to minimize impact on the tape-out schedule.

Timing Closure

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Lastly, let’s talk about timing closure. Why do you think this is vital during the tape-out?

I think it’s about ensuring that all signals meet their timing requirements?

Correct! Timing closure is about making sure that there are no timing violations left in the design. A mnemonic to keep this in mind is 'Timely Designs Save Time'. Achieving timing closure is crucial because missed violations can lead to serious operational failures.

What happens if we don’t achieve timing closure before tape-out?

You could end up delaying production or requiring extensive rework, which can be costly. In summary, timing closure is a non-negotiable milestone for successful tape-out—it's all about ensuring each part of the design functions as expected under timing constraints.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section highlights the various challenges encountered during the tape-out process in VLSI design. These challenges include ensuring the design is error-free after all optimizations, managing last-minute design changes, and achieving timing closure, which is crucial for successful tape-out. These elements are vital as they can impact the schedule and the functional integrity of the chip once fabricated.

Detailed

Challenges During Tape-Out

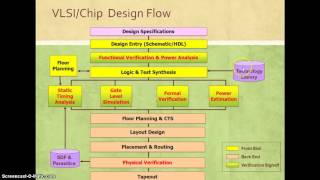

The tape-out process is the final step before sending a chip design to a semiconductor foundry for fabrication. This phase comes with its own set of challenges that can significantly impact the overall project timeline and design integrity.

- Final Verification: After completing all optimizations—such as placement and routing—designers must perform rigorous checks to ensure that the design is free from any errors. Minor mistakes overlooked during earlier stages can escalate into critical failures if not caught at this point.

- Last-Minute Design Changes: It is not uncommon for designers to need to incorporate changes at this stage, which could necessitate substantial rework. These urgent modifications often require additional verification steps, putting further pressure on the timeline.

- Timing Closure: Achieving timing closure is essential for a successful tape-out. It involves ensuring that there are no remaining timing violations in the design, which could lead to functional failures once the chip is in operation. Delays in achieving timing closure can push back the entire tape-out schedule, risking additional costs and setbacks in production.

These challenges underscore the importance of thoroughness and meticulous attention to detail in the tape-out process to facilitate a smooth transition from design to fabrication.

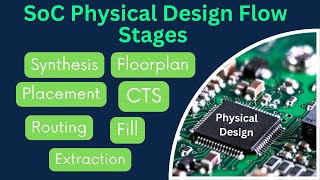

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Final Verification Challenges

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Final Verification: Ensuring that the design is error-free after all optimizations, placement, and routing is completed. Small errors that were previously unnoticed can become significant during the final stages.

Detailed Explanation

Final verification is the process of checking that the chip design has no errors before it is finalized for manufacturing. This step is crucial because, after all adjustments to the design are made, any overlooked errors can potentially become major issues that impact the functionality of the chip. Designers must carefully review every aspect to ensure it meets all specifications.

Examples & Analogies

Imagine preparing for an important exam. After studying hard and making revisions, you go through your notes one last time to catch any small mistakes that could jeopardize your chances of passing. Just like in exam prep, final verification in design helps to identify any errors and get everything in order before the final submission.

Last-Minute Design Changes

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Last-Minute Design Changes: Sometimes, design changes are needed late in the process, which could require significant rework and additional verification steps.

Detailed Explanation

Occasionally, as the tape-out deadline approaches, designers may identify new changes that need to be made to the chip. These modifications, if they occur late in the process, can be particularly challenging because they may require revisiting previous checks and validations that have already been completed. This can lead to delays, as additional time is needed to ensure that these last-minute changes do not introduce new errors.

Examples & Analogies

Think of baking a cake. If you realize at the last moment that you forgot to add sugar, you must go back and mix it into the batter. This means you have to mix it all over again, bake it for the right time again, and check it carefully to ensure it tastes good. In design, similar last-minute changes can create chaos if not handled carefully.

Timing Closure Challenges

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Timing Closure: Achieving timing closure and ensuring that no timing violations remain is crucial for a successful tape-out. Delays in timing closure may push back the tape-out schedule.

Detailed Explanation

Timing closure refers to the process of ensuring that all timing requirements are met in the chip design. This is important because if timing requirements are violated, the chip may not operate correctly. Verifying timing can be complex as many factors can affect it, and if not managed well, this can lead to delays in the final tape-out process. Achieving timing closure is essential to keep the project on schedule.

Examples & Analogies

Think of a train schedule where all trains must arrive and leave on time. If one train is late due to delays, it can mess up the entire schedule for that day, making it difficult to manage the other trains. In chip design, ensuring everything 'arrives on time' means the chip will function reliably when it is finally manufactured.

Key Concepts

-

Final Verification: The essential backup check for any errors before tape-out.

-

Last-Minute Design Changes: Essential amendments that need to be managed effectively.

-

Timing Closure: Ensuring that all timing requirements are met to prevent functional issues.

Examples & Applications

An instance of last-minute changes is when a client requests additional functionality just days before the tape-out deadline.

A potential error might be a missed signal path that should connect two components, which could lead to malfunctioning in the final product.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Before the last check, keep it neat, or designs may cause a defeat.

Stories

Imagine a chef preparing a meal who must check all ingredients before serving; any oversight could spoil the dish—just like ensuring verification before tape-out.

Memory Tools

F-L-T: Final verification, Last-minute changes, Timing closure.

Acronyms

VLT

Verify

Last-minute

Timing–the key aspects to remember during tape-out.

Flash Cards

Glossary

- TapeOut

The final stage in the VLSI design process where the finalized design is sent for fabrication.

- Final Verification

The last round of checks performed to ensure a design has no errors before tape-out.

- LastMinute Design Changes

Adjustments to the design that are made shortly before tape-out, often necessitating rework.

- Timing Closure

The process of ensuring all parts of the circuit meet timing requirements before fabrication.

Reference links

Supplementary resources to enhance your learning experience.