Design Rule Checking (DRC)

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to DRC

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome, everyone! Today, we’re diving into Design Rule Checking, or DRC for short. Who can tell me what they think DRC involves?

I think it’s about checking if the design follows certain rules?

Exactly! DRC ensures that the chip layout complies with manufacturing specifications. These rules encompass things like spacing and width of features on the chip.

What happens if the layout doesn’t follow these rules?

Good question! If there’s a violation, it can lead to issues like manufacturing defects and reliability problems. Think of it as leading to costly design errors down the line.

So, it’s really important for the final chip's functioning?

Absolutely! DRC is a critical checkpoint in the design process that helps us catch issues before production.

How do we perform DRC checks?

That's where EDA tools like Cadence Calibre come in. They automate the checking process to quickly flag any violations that need correction.

In summary, DRC is essential to ensure that our chip will work correctly after fabrication.

DRC Violations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s delve deeper into what constitutes a DRC violation. Can anyone provide an example?

Maybe if two metal traces are too close to each other?

Exactly! Insufficient spacing can cause overlap, leading to short-circuits during manufacturing. Other examples include wires being too thin.

What’s the consequence of these violations?

Great question! Such violations can severely impact the chip's functionality and lifetime by causing defects or signal integrity problems.

Can DRC checks prevent all problems?

While DRC is very effective, it can only catch design rule-related errors. We complement it with other checks like LVS and ERC for comprehensive verification.

So remember, understanding and resolving DRC violations is critical for producing reliable chips!

Tools for DRC

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s discuss the tools used to perform DRC checks. Can anyone name a few?

I know Cadence Calibre is one of them!

That’s right! Cadence Calibre, Mentor Graphics PADS, and Synopsys IC Validator are just a few examples of specialized EDA tools.

How do these tools actually help?

These tools automatically check the design against the manufacturing rules, quickly highlighting any violations that designers must address.

Do they provide reports for violations?

Yes, they generate detailed reports that help designers locate and rectify issues efficiently.

In summary, using EDA tools ensures that DRC checks are thorough and efficient, preventing costly errors in the fabricating phase.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Design Rule Checking (DRC) is an essential method in VLSI design verification, focusing on ensuring that the chip layout complies with manufacturing constraints. It identifies layout violations that could cause operational issues, leveraging specialized EDA tools for automated checks.

Detailed

Detailed Summary of Design Rule Checking (DRC)

Design Rule Checking (DRC) is a fundamental method in the physical design verification process of VLSI circuits. The primary aim of DRC is to ensure that the physical layout of the chip adheres to specific manufacturing rules set forth by the semiconductor foundries. These rules specify key parameters such as minimum allowable distances between components, the width of wires, and other critical design constraints for various features like transistors, metal layers, and vias.

Key Components:

- DRC Violations: If a layout fails to meet these specifications—for example, by having metal traces that are too close together or wires that are too thin—these discrepancies are flagged as DRC violations. Such violations can ultimately lead to manufacturing defects, signal integrity issues, or reduced reliability of the final product.

- Tools for DRC: DRC is generally undertaken with specialized Electronic Design Automation (EDA) software. Popular tools include Cadence Calibre, Mentor Graphics PADS, and Synopsys IC Validator, which automate the checking of design against the manufacturing rules. These tools provide comprehensive reports highlighting any violations that need correction.

In summary, DRC effectively plays a pivotal role in ensuring design correctness prior to the fabrication of chips, thus safeguarding against potential costly errors during the manufacturing process.

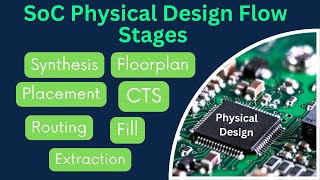

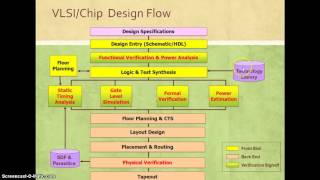

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of DRC

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Design Rule Checking (DRC) is a process that ensures that the layout of the chip adheres to the manufacturing rules specified by the semiconductor foundry. These rules define the minimum allowable spacing, width, and other design constraints for features such as transistors, metal layers, and vias.

Detailed Explanation

Design Rule Checking (DRC) is a verification process used in the design of integrated circuits to ensure that the layout conforms to specific manufacturing rules. These rules are set by the semiconductor foundry and specify critical parameters such as how close two components can be, the minimum width of wires, and the allowed shapes of geometries on the chip. The main goal of DRC is to prevent errors that can occur during the manufacturing process, which might lead to defects in the final product.

Examples & Analogies

Think of DRC like a building inspector who makes sure that a construction project follows local building codes. Just as the inspector checks for proper spacing between windows and doors to ensure safety and compliance, DRC checks the chip layout for compliance with manufacturing rules to ensure that the chip operates correctly.

Understanding DRC Violations

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

DRC Violations: If a layout feature violates these design rules (e.g., insufficient spacing between metal traces or too narrow a wire), a DRC violation is flagged. These violations can lead to manufacturing defects, signal integrity problems, or reliability issues.

Detailed Explanation

When a layout design does not conform to the established manufacturing rules, it is labeled as a DRC violation. Common examples of such violations include metal traces that are too close together or wires that are narrower than allowed. These discrepancies can result in serious problems when the chip is manufactured: they may cause short circuits, disrupt signal flow, or create weak points that are prone to failure. Identifying and fixing these violations before fabrication is crucial to ensure the chip's performance and longevity.

Examples & Analogies

Imagine a crowded highway where cars are too close to each other; this would increase the risk of accidents. Similarly, in a chip layout, if the components are placed too close together, they risk interfering with each other's signals, leading to potential failures. Just as traffic laws are designed to ensure safety on the roads, DRC rules ensure safe and effective layouts for chips.

Tools for DRC

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Tools for DRC: DRC is typically performed using specialized EDA tools that automatically check the design against the manufacturing process rules. Tools like Cadence Calibre, Mentor Graphics PADS, and Synopsys IC Validator are widely used for DRC checks.

Detailed Explanation

To perform DRC efficiently and effectively, engineers use Electronic Design Automation (EDA) tools. These software tools automate the checking process, comparing the chip's layout against the defined design rules. If they detect violations, they notify the designer, allowing corrections to happen before the design progresses to manufacturing. Common EDA tools include Cadence Calibre, Mentor Graphics PADS, and Synopsys IC Validator, each designed to facilitate comprehensive and accurate DRC processes.

Examples & Analogies

Consider how software applications can run spell-checks to identify and correct writing errors. Similarly, DRC tools act like spell-checkers for chip designs, quickly identifying issues that could lead to manufacturing mistakes, allowing designers to correct them before 'sending' their design to be fabricated.

Key Concepts

-

DRC Definition: A crucial process in the VLSI design process focused on ensuring the layout complies with manufacturing rules.

-

Importance of DRC: Essential for preventing costly manufacturing defects and ensuring chip reliability.

-

Automation with Tools: EDA tools automate DRC checks to streamline the verification process.

Examples & Applications

If two metal traces are spaced less than the minimum allowed, it can result in a short circuit when the chip is fabricated.

A transistor width below the minimum specification could lead to insufficient current flow, resulting in malfunction.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To avoid a chip that's flawed, check its layout, give it a nod.

Stories

Imagine a chef meticulously measuring ingredients. If they use too much salt, it ruins the dish—just like ignoring DRCs can ruin a chip's functionality.

Memory Tools

Remember 'SILVER' for DRC checks: Spacing, Integrity, Layering, Voltage, Elements, Rules.

Acronyms

DRC

Design Rules Confirmed.

Flash Cards

Glossary

- Design Rule Checking (DRC)

A process ensuring that the layout of the chip adheres to the manufacturing rules defined by semiconductor foundries.

- DRC Violations

Errors in the layout that violate specified design rules, potentially causing manufacturing defects.

- EDA Tools

Software used in electronic design automation to check and verify the design layout against required specifications.

- Signal Integrity

The quality of electrical signals in a circuit, which can be degraded by issues like interference and noise.

Reference links

Supplementary resources to enhance your learning experience.