Overview of the Tape-Out Process

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Preparation for Tape-Out

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Alright, everyone! Let's begin with the preparation needed before tape-out. Can anyone tell me what steps must be fulfilled?

Isn't it about running final checks like DRC, LVS, and ERC?

Exactly! DRC stands for Design Rule Checking, LVS is Layout Versus Schematic, and ERC is Electrical Rule Checking. These ensure that there are no remaining violations before we proceed with GDSII file generation.

What happens if there are violations found?

Great question! If any violations appear, they must be fixed immediately. Remember, think about the acronym 'VFG' - Verify, Fix, and Generate. What does generating mean in this context?

It refers to creating the GDSII files!

Perfect! The GDSII files encapsulate all required information for fabrication. Lastly, let's not forget the importance of handing the design to the foundry seamlessly.

Does the foundry check for errors too?

Yes, indeed! The foundry performs its checks to confirm that the design can be successfully fabricated. Great participation today! Let's summarize: we discussed the importance of final checks, design handoff, and what the outcomes are.

Challenges During Tape-Out

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s address the challenges we might encounter during tape-out. Who can identify some of those challenges?

I think one challenge is ensuring the design remains error-free at the last minute.

Correct! Final verification is key, as small unnoticed errors can become critical. What’s another challenge?

Last-minute design changes could be tricky too!

Exactly! Such changes require significant revisiting of the design and additional checks. Now, let’s discuss timing closure. How important is it for tape-out?

It’s crucial because if timing violations remain, it could delay everything.

Absolutely! Timing closure ensures that all timing requirements are met before we tape-out. To memorize challenges, think of 'LET': Last-minute changes, Error checks, and Timing closure. Recap for us what what 'LET' stands for?

Last-minute changes, Error checks, and Timing closure!

Exactly right! The balance of these factors is essential as we approach tape-out.

Tape-Out Sign-Off

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s talk about tape-out sign-off. Why is this step crucial?

It’s the official approval for the chip design before sending it for fabrication.

Exactly! Tape-out sign-off involves ensuring that DRC, LVS, and ERC are all passed. Why do we check for timing and power requirements?

To ensure the design is functional under all expected conditions, right?

Correct! Think about it as the final exam for your design. Ensuring everything meets requirements before ‘going to the real world.’ How do we summarize the key elements of sign-off?

DRC, LVS, ERC success, timing, and power checks!

Excellent! And don’t forget documentation; it’s critical that everything from GDSII files to reports is conclusively gathered. Let's end this session by recapping everything related to tape-out sign-off.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Tape-out marks the transition from design to fabrication in the VLSI design process. It involves thorough checks and the generation of GDSII files, ensuring the design meets all specifications before manufacturing. Challenges include final error verification, last-minute design changes, and timing closure.

Detailed

Overview of the Tape-Out Process

The tape-out process represents the final and critical phase in the VLSI design cycle before sending the chip design to a semiconductor foundry for fabrication. It culminates in the creation of GDSII (Graphic Data System II) files, which encapsulate the comprehensive physical layout of the chip, including metal layers, transistors, and other integral features.

Preparation for Tape-Out

Before tape-out, several essential steps are necessary:

- Final DRC, LVS, and ERC Checks: A comprehensive round of physical design verification is mandatory to ensure no violations exist. Any outstanding DRC, LVS, or ERC violations must be resolved pre-tape-out.

- Sign-Off Verification: Conduct final rundowns that include timing checks, power analysis, and signal integrity checks, ensuring the chip's operational capability under real-world circumstances.

- GDSII File Generation: The last design data is converted to GDSII format, an industry standard that encompasses all fabrication requirements, including layer definitions and geometries.

- Design Handoff to Foundry: The generated GDSII files are forwarded to the semiconductor foundry for chip fabrication, which then performs additional manufacturing checks to confirm that the design can be effectively fabricated.

Challenges During Tape-Out

The tape-out process is not without its challenges:

- Final Verification: Ensuring the design is devoid of errors following optimization, placement, and routing is crucial. Minor unnoticed errors can transform into significant issues during final stages.

- Last-Minute Design Changes: The necessity for late-stage design alterations might incur substantial rework and further verification tasks.

- Timing Closure: Achieving timing closure while confirming no existing timing violations is pivotal for a triumphant tape-out. Timing closure delays might disrupt the schedule.

Tape-Out Sign-Off

Tape-out sign-off involves the formal agreement from the design team signaling readiness for fabrication, encompassing:

- DRC, LVS, and ERC Sign-Off: Final verifications to ensure the design is compliant with manufacturing rules and free from layout or electrical errors.

- Timing and Power Sign-Off: Confirmation that the design meets timing and power requisites across multiple process corners and operating conditions.

- Documentation: Finalizing necessary documentation, including GDSII files and timing/power analysis reports, that will accompany the files to the foundry.

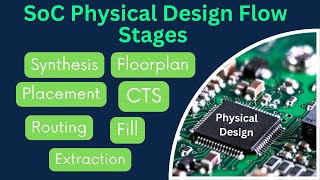

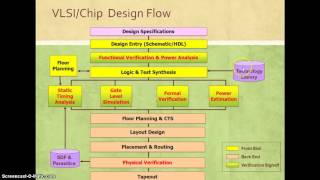

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Tape-Out

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Tape-out is the final step in the VLSI design process before the chip is sent to the semiconductor foundry for fabrication. It involves the generation of the final GDSII (Graphic Data System II) files, which describe the physical layout of the chip, including all layers of metal, transistors, vias, and other features.

Detailed Explanation

The tape-out process is crucial because it marks the transition from design to manufacturing. Before the chip can be fabricated, designers must ensure that all necessary files are prepared and contain accurate information regarding the chip's layout. GDSII files serve as the blueprint for the foundry, detailing every component and layer of the integrated circuit. This step is akin to finalizing construction blueprints before a building can be built.

Examples & Analogies

Imagine planning to build a house. Before construction begins, you would need a complete and detailed blueprint that shows every room, electrical system, and plumbing. Just like this blueprint is critical for the construction crew to follow, GDSII files are essential for semiconductor fabrication to accurately produce the chip.

Preparation for Tape-Out

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Before tape-out, the following steps must be completed:

● Final DRC, LVS, and ERC Checks: A final round of physical design verification must be performed to ensure that no violations exist. Any remaining DRC, LVS, or ERC violations must be fixed before the design can be taped-out.

● Sign-Off Verification: The design undergoes final verification, including timing checks (STA), power analysis, and signal integrity checks to ensure that the chip will operate as expected under real-world conditions.

● GDSII File Generation: The final design data is converted into the GDSII format, which is the industry standard for representing the layout of integrated circuits. This file contains all the information required for fabrication, including layer definitions and geometry.

● Design Handoff to Foundry: Once the GDSII files are generated, they are sent to the semiconductor foundry, where they will be used to fabricate the chip. The foundry performs additional manufacturing checks to ensure the design can be fabricated successfully.

Detailed Explanation

Preparing for tape-out involves several important steps. Firstly, designers must conduct thorough checks to ensure that the design conforms to design rules (DRC), is consistent with the schematic (LVS), and meets electrical requirements (ERC). Following this, a final verification is conducted that includes timing and power analyses to confirm that the chip will function as intended once manufactured. The design information is then compiled into the GDSII format, which the foundry uses for fabrication. Finally, the verified GDSII files are handed off to the semiconductor foundry to begin the manufacturing process.

Examples & Analogies

Think of preparing for a big presentation. Before you present, you check your slides for any mistakes (like DRC checks), ensure they're in the right order (like LVS checks), and practice your delivery to meet the time limit (like ERC checks). Once everything is perfect, you save your presentation file (like GDSII file generation) and send it to the event coordinator (like design handoff to foundry). These steps ensure that your presentation goes smoothly, just like the preparation required for successful tape-out.

Challenges During Tape-Out

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The tape-out process comes with its own set of challenges:

● Final Verification: Ensuring that the design is error-free after all optimizations, placement, and routing is completed. Small errors that were previously unnoticed can become significant during the final stages.

● Last-Minute Design Changes: Sometimes, design changes are needed late in the process, which could require significant rework and additional verification steps.

● Timing Closure: Achieving timing closure and ensuring that no timing violations remain is crucial for a successful tape-out. Delays in timing closure may push back the tape-out schedule.

Detailed Explanation

Tape-out poses several challenges that can impact the success of the design process. During final verification, designers must meticulously check every aspect of the design to identify and resolve any lingering issues. This is challenging because small mistakes can be easily overlooked, yet they can have major consequences later. Additionally, late design changes can complicate the process further, requiring extra checks that can jeopardize timelines. Finally, ensuring that timing requirements are met is critical; any delays here can postpone the entire tape-out schedule.

Examples & Analogies

Consider planning a wedding. In the last days before the event, you must double-check everything to ensure it's perfect (final verification). Suddenly, you may decide to change the venue or guest list (last-minute design changes), which makes everything more complicated and requires urgent adjustments (more verification). Lastly, if you're running behind schedule on organizing everything (timing closure), it can stress you out and may affect the big day. Just like in a wedding, the tape-out process requires close attention to detail and time management to ensure success.

Tape-Out Sign-Off

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Tape-out sign-off is the formal approval from the design team that the chip design is ready for fabrication. It involves final checks and verifications to ensure the design meets all specifications and that the chip is manufacturable. The tape-out sign-off typically includes:

● DRC, LVS, and ERC Sign-Off: Final verification checks to ensure that the design adheres to manufacturing rules and is free of electrical or layout errors.

● Timing and Power Sign-Off: Ensuring that the design meets all timing and power requirements across all process corners and operating conditions.

● Documentation: Finalizing all documentation, including GDSII files, timing reports, and power analysis reports, to be sent to the foundry.

Detailed Explanation

The tape-out sign-off is a pivotal moment in the design process, as it represents the final approval to proceed with chip fabrication. This step includes comprehensive checks of design compliance, confirming that the design adheres to all relevant manufacturing standards (DRC, LVS, ERC) and confirming that its performance meets specified requirements (timing and power). Additionally, the required documentation is finalized so that the foundry has everything necessary for successful fabrication. This formal sign-off ensures that everyone is on the same page before moving forward with production.

Examples & Analogies

Think of the tape-out sign-off as the final approval stage before publishing a book. The editors check every chapter for errors (DRC, LVS, ERC checks), verify that the content follows the overall theme and flow (timing and power checks), and finally, the manuscript is prepared and formatted for printing (documentation). Only after these steps does the publisher give the ‘green light’ to print the book, ensuring it’s ready for readers. Similarly, the tape-out sign-off ensures that the chip design is fully verified and ready for fabrication.

Key Concepts

-

Tape-Out: The process of finalizing designs and transitioning to manufacturing.

-

GDSII: The file format for layout information required for chip fabrication.

-

Final Verification: Essential checks like DRC, LVS, and ERC that ensure a design is free of errors.

Examples & Applications

Example 1: A computer chip design reaches tape-out, confirming all previous iterations and checks before generating its GDSII files.

Example 2: A design fails DRC checks before tape-out due to insufficient spacing between metal traces, which delays the manufacturing schedule.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Before we tape it out, be sure no doubt, with final checks about!

Stories

Imagine a chef finalizing a recipe before a big event, ensuring every ingredient is perfect; just as a design must pass final checks before tape-out.

Memory Tools

Remember the acronym 'SGC' for Tape-Out Sign-Off: Sign-off lists include: Sign-off, Generate files, Confirm that the design meets specs.

Acronyms

Use 'FDR' for Final checks

Final DRC

Final LVS

and Final ERC.

Flash Cards

Glossary

- TapeOut

The final stage in the VLSI design process where designs are finalized and sent to fabrication as GDSII files.

- GDSII

Graphic Data System II, the file format used for representing the layout of integrated circuits.

- DRC

Design Rule Checking; a verification process that checks whether the design adheres to manufacturing rules.

- LVS

Layout Versus Schematic; a verification process ensuring that the layout corresponds to the schematic design.

- ERC

Electrical Rule Checking; checks for electrical correctness and behavior of the design.

Reference links

Supplementary resources to enhance your learning experience.