Introduction to Physical Design Verification

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of Physical Design Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we are discussing physical design verification. This is a vital component of VLSI design. Can anyone tell me why verification is necessary?

I think it's to make sure the chip works properly after it's made.

Exactly! Verification ensures the chip adheres to design specifications, preventing expensive errors during manufacturing. Remember: ‘Verify to Avoid’ costs!

What kind of errors can happen if we skip this step?

Skipping verification can lead to functional failures or reliability issues in the chip. It’s crucial for both performance and manufacturability.

So, how does physical design verification actually work?

Great question! We’ll dive deeper into specific methods soon like DRC, LVS, and ERC.

What does each of those acronyms stand for?

DRC is Design Rule Checking, LVS is Layout Versus Schematic, and ERC is Electrical Rule Checking—these are critical methods in this verification process.

To summarize, physical design verification ensures that our designs function as expected, minimizing costly errors.

Methods of Verification

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's delve into the three main methods of verification. First is DRC. Can someone describe what it does?

DRC checks if the layout meets manufacturing rules.

Right! It checks spacing and width of designs to avoid issues like shorts or breaks. How about LVS? What does it ensure?

LVS compares the layout to the schematic, right?

Exactly! It verifies that everything is connected properly. Now, can anyone explain ERC?

ERC checks electrical behavior, like power integrity.

Correct! It looks for issues that would affect the chip’s functionality. Remember: DRC, LVS, and ERC are fundamental for successful chip design.

In summary, understanding these verification methods is essential for creating functional and reliable VLSI designs.

Overview of the Tape-Out Process

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's talk about the tape-out process. Why do you think this is the final step before fabrication?

Because it finalizes the design files for manufacturing?

Exactly! Tape-out is where we generate GDSII files, crucial for the fabrication process. Can anyone remember what GDSII stands for?

Graphic Data System II!

Correct! This format describes all layout data. What must be verified before tape-out?

Final checks like DRC, LVS, and ERC need to be done.

Right again! If any violations remain, the design can't go to fabrication. In summary, tape-out is critical as it represents the transition from design to manufacturing.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section introduces physical design verification in the VLSI design process, emphasizing its importance in confirming that a chip's physical layout adheres to design specifications and manufacturing rules. Key verification methods that will be explored include Design Rule Checking (DRC), Layout Versus Schematic (LVS), and Electrical Rule Checking (ERC), culminating in the tape-out process that transforms the design into a manufacturable product.

Detailed

Introduction to Physical Design Verification

Physical design verification is a critical step in the VLSI (Very Large Scale Integration) chip design process. It serves the essential function of ensuring that the physical layout of the chip aligns with the specified design requirements and manufacturing rules. This verification process is vital to confirm that the chip will function correctly post-fabrication, helping to prevent costly design errors that can arise during manufacturing.

The primary objective of physical design verification involves checking the layout against various constraints; these include design rules, timing, power, and manufacturability. This chapter will delve into the core methods of physical design verification:

- Design Rule Checking (DRC): Ensures adherence to manufacturing rules.

- Layout Versus Schematic (LVS): Confirms that the layout matches the schematic.

- Electrical Rule Checking (ERC): Verifies electrical behaviors against specified requirements.

Moreover, we will briefly discuss the tape-out process, which is the final step before sending the chip design for fabrication.

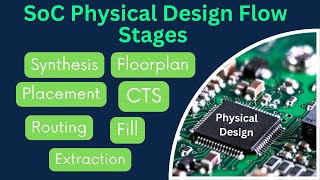

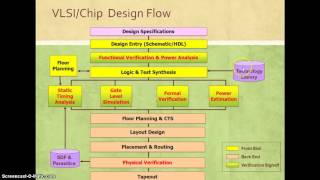

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Importance of Physical Design Verification

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Physical design verification is a critical step in the VLSI design process that ensures that the physical layout of a chip adheres to the design specifications and manufacturing rules.

Detailed Explanation

Physical design verification plays a crucial role in the VLSI (Very Large Scale Integration) design process. It involves checking that the layout of the chip matches specific requirements and complies with manufacturing standards. This step ensures that once the chip is fabricated, it will operate correctly, preventing costly errors that might arise during manufacturing.

Examples & Analogies

Think of physical design verification like quality control in a car manufacturing plant. Just as cars are checked for safety and functionality before they hit the road, chips need to be verified to ensure they will work properly once produced.

Objectives of Physical Design Verification

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Verification ensures that the chip will function correctly when fabricated, avoiding costly design errors that may arise during manufacturing.

Detailed Explanation

The main goal of physical design verification is to confirm that the chip's layout is correct and follows various necessary constraints. This includes observing design rules (like spacing between components), timing requirements (how quickly signals must travel through the chip), power efficiency, and manufacturability (how easily the chip can be produced on the factory floor).

Examples & Analogies

Consider a blueprint for a building. Before construction begins, it must be verified that the design conforms to safety codes and practical considerations. Physical design verification of a chip serves the same purpose, ensuring that everything is in order before manufacturing starts.

Methods for Physical Design Verification

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this chapter, we will explore the methods for physical design verification, including Design Rule Checking (DRC), Layout Versus Schematic (LVS), and Electrical Rule Checking (ERC).

Detailed Explanation

The chapter outlines several methods to confirm that the chip design is correct. Design Rule Checking (DRC) focuses on ensuring the layout follows specific spacing and size rules. Layout Versus Schematic (LVS) checks that the physical design matches the circuit's intended logic. Electrical Rule Checking (ERC) verifies that electrical properties comply with design requirements. Each method targets a different aspect of the design to ensure comprehensive verification.

Examples & Analogies

Imagine preparing a recipe: first, you check that you have all the ingredients (like DRC), then you make sure you're following the steps correctly (like LVS), and finally, you taste the dish to ensure the flavors are balanced before serving it (like ERC).

The Tape-Out Process Overview

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

We will also cover the tape-out process, the final step in the design cycle before sending the chip design to fabrication.

Detailed Explanation

Tape-out is the last stage in the chip design cycle, where the finalized design is prepared for manufacturing. This step involves generating GDSII files, which detail the physical layout of the chip, including all components and layers. After completing verification processes, the design is ready to be sent to the foundry to begin the production of the physical chip.

Examples & Analogies

Think of tape-out like finalizing a book for printing. After rounds of editing and proofreading, the manuscript is converted into a print-ready format and sent to the publisher for mass production. Similarly, tape-out prepares the chip design for the manufacturing process.

Key Concepts

-

Physical Design Verification: Ensuring adherence to design and manufacturing specifications.

-

Design Rule Checking (DRC): Checking layout against manufacturing rules.

-

Layout Versus Schematic (LVS): Verifying layout matches schematic.

-

Electrical Rule Checking (ERC): Confirming electrical behavior meets design requirements.

-

Tape-Out: Preparing final design files for fabrication.

Examples & Applications

Example of DRC violation: Insufficient spacing between two metal traces leading to shorts.

Example of LVS violation: Incorrect transistor connections causing functional inaccuracies.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Verify to avoid, let mistakes be destroyed!

Stories

Imagine a chef preparing a dish. Before serving, they check the recipe to ensure every ingredient is right. That's like physical design verification, making sure the chip will work as intended.

Memory Tools

Remember DRC, LVS, ERC: 'Don't Let Errors Rule!'

Acronyms

LVS = Layout Validates Schematic.

Flash Cards

Glossary

- Physical Design Verification

The process ensuring that a chip's physical layout meets design specifications and manufacturing rules.

- Design Rule Checking (DRC)

A verification method that checks the chip layout against manufacturing rules regarding spacing, width, and other constraints.

- Layout Versus Schematic (LVS)

A method that ensures the physical layout of a circuit matches its intended logical schematic.

- Electrical Rule Checking (ERC)

A verification method that checks the electrical behavior of the design against specified requirements.

- TapeOut

The final phase in the VLSI design process where design files are prepared for semiconductor fabrication.

- GDSII

Graphic Data System II, an industry-standard format for representing the layout of integrated circuits.

Reference links

Supplementary resources to enhance your learning experience.