Timing Analysis Verification

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Timing Analysis

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will cover timing analysis verification, which ensures that the layout of our chip meets essential timing constraints. Can anyone tell me why timing is critical in digital circuits?

Timing is crucial because if components do not receive signals at the correct time, they might process incorrect data.

Exactly! Misalignment in timing can lead to setup or hold violations, which can cause erroneous behavior in sequential circuits. What do you think might happen if we exceed the allowable delay?

It could mean that a flip-flop latches incorrect data, affecting the entire operation of the circuit.

Good insight! Timing verification is vital for maintaining system integrity. At the core of this process is static timing analysis. Can anyone explain what that involves?

Static Timing Analysis (STA)

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Static timing analysis, or STA, checks the timing of all signal paths in a design, from registers to combinational logic. Why do you think it’s 'static'?

Because it analyzes the timing based on a fixed design without simulating real-time operation.

Great point! STA can help identify critical paths, which are the longest delay paths in a design. Does anyone know any tools used for STA?

I've heard of Synopsys PrimeTime. Is that one of the tools?

Yes! Synopsys PrimeTime is a widely used tool for timing verification. It helps ensure that the design adheres to the required timing constraints after placement and routing.

Understanding Timing Violations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s talk about timing violations. Can anyone define what a timing violation is?

A timing violation occurs when a critical path delay exceeds the limit set for setup or hold times, right?

Exactly! These violations can lead to incorrect latching of data. What are some consequences of allowing such violations?

The circuit may fail to operate as desired and might even result in chip failures.

Absolutely! Preventing timing violations is essential for reliability in VLSI design.

Using Timing Verification Tools

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand timing analysis, let’s explore how we can use tools like Cadence Tempus and Synopsys PrimeTime. Has anyone had experience using these tools?

I haven’t used them, but I know they check timing constraints and provide timing reports.

Correct! These tools analyze the design after placement and routing to ensure timing constraints are satisfied. What might be included in a timing report?

I think it would likely include details about setup times, hold times, and any timing violations found.

Exactly! The reports help optimize the design if violations are detected. Ensuring timing integrity is crucial for the chip's functionality.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

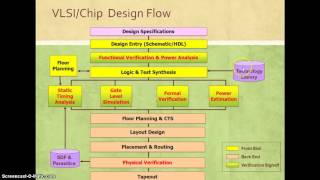

This section covers the timing analysis verification process, focusing on how it examines the chip layout for compliance with timing constraints, including setup and hold times, propagation delays, and clock skew, and discusses tools used to perform these checks.

Detailed

Detailed Summary

Timing analysis verification is a crucial aspect of the physical design verification process in VLSI design. It focuses on ensuring that the chip layout adheres to timing constraints such as setup times, hold times, propagation delays, and clock skew. This verification is essential to prevent functional errors in sequential circuits, especially those relying on proper timing.

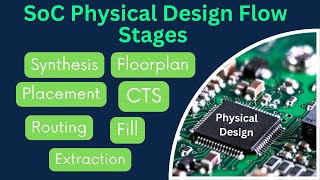

The process typically involves static timing analysis (STA), which evaluates the timing of signal paths throughout the design, examining paths from registers through to the combinational logic.

Key Points:

- Timing Violations: Timing violations occur when the delay along a critical path exceeds the allowable limit, which can lead to data being latched incorrectly by flip-flops.

- Tools for Timing Verification: There are specialized EDA tools available for timing verification, such as Synopsys PrimeTime and Cadence Tempus, which check the timing constraints post placement and routing.

In conclusion, effective timing analysis verification is vital for ensuring that VLSI designs function correctly under varying operational conditions and that all timing requirements are fulfilled.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of Timing Verification

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing verification ensures that the layout meets the required timing constraints, including setup and hold times, clock skew, and propagation delay.

Detailed Explanation

Timing verification is a critical process in ensuring that all signals within the electronic circuit are processed in the correct time frames. It checks whether the design adheres to specific timing constraints that are essential for its proper operation. These constraints include 'setup time' (the time before the clock edge when data must be stable), 'hold time' (the time after the clock edge when data must remain stable), 'clock skew' (the difference in timing for clock signal reaching different components), and 'propagation delay' (the time it takes for a signal to travel from one point to another in the circuit). Ensuring that all these aspects meet the necessary requirements prevents malfunctioning of the circuit during operation.

Examples & Analogies

Think of timing verification like a conductor leading an orchestra. Each musician (or circuit component) must play their notes at the right time to create a harmonious piece of music. If one musician starts playing too early or too late (violating timing constraints), the music won’t sound right, just like if a circuit component doesn’t pass its timing checks, the circuit would malfunction.

Timing Violations Explained

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing violations occur when the delay along a critical path exceeds the allowable time, leading to setup or hold violations, which could cause incorrect data to be latched by flip-flops.

Detailed Explanation

Timing violations happen when the delays in signal processing exceed the limits defined by the timing analysis. These critical paths are the routes that data signals travel through the circuit. If the delay is too long, it can result in data being read too early (setup violation) or being read too late (hold violation) by a flip-flop – a type of memory in the circuit. This means that the correct data may not be saved or processed, causing failure in the circuit operations.

Examples & Analogies

Imagine trying to catch a ball thrown to you but you look away for a moment. If the ball arrives when your eyes are not on it, you might miss catching it entirely; this is similar to what happens in a timing violation when the data arrives either too early or too late.

Tools for Timing Verification

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Tools like Synopsys PrimeTime and Cadence Tempus are widely used for timing analysis, checking the timing constraints of the design and ensuring that they are met after placement and routing.

Detailed Explanation

To perform timing analysis effectively, engineers use specialized software tools. Synopsys PrimeTime and Cadence Tempus are two popular tools that automate the timing verification process. They analyze the timing paths in the design to identify potential timing violations and ensure all signals meet the timing constraints determined during design. Using these tools saves engineers time and reduces the risk of human error in calculating the timing.

Examples & Analogies

Think of these tools as pacing coaches for runners in a race. Just as a coach helps runners understand the best times to speed up or slow down during training, timing tools help circuit designers understand how to manage the timing in their designs to avoid errors during operation.

Key Concepts

-

Static Timing Analysis (STA): A technique for validating timing constraints in circuit design without simulating dynamic behavior.

-

Timing Violations: Conditions where delays exceed limits, causing functional errors.

-

Clock Skew: Variation in clock signal arrival times affecting synchronization.

-

Propagation Delay: Time taken for a signal to propagate through a circuit.

Examples & Applications

In a sequential circuit, if a flip-flop receives data too late due to timing violations, it may latch incorrect values, leading to circuit failure.

Using Synopsys PrimeTime, designers can generate timing reports that highlight critical paths and violations, guiding further optimizations.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Timing's key, don't let it stray, or data won't latch the right way.

Stories

Imagine a race where two cars start at different times. The car that starts later might miss the finish line. Similarly, clock skew can mean components miss their data latching time.

Memory Tools

To remember timing concepts: 'SVC' - Setup, Violation, Clock-skew.

Acronyms

STA - Static Timing Analysis helps remember, 'Stay Timed Accurately.'

Flash Cards

Glossary

- Static Timing Analysis (STA)

A method used to validate timing constraints in a digital circuit design by analyzing all paths without simulating dynamic behavior.

- Timing Violations

Occur when a signal path's delay exceeds allowable limits, leading to potential errors in data latching in sequential circuits.

- Clock Skew

The difference in arrival times of the clock signals to different components in a circuit, which can lead to timing issues.

- Propagation Delay

The time it takes for a signal to travel through a circuit from one point to another.

Reference links

Supplementary resources to enhance your learning experience.