Layout Versus Schematic (LVS)

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to LVS

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we will discuss Layout Versus Schematic (LVS), a critical component in physical design verification. Could anyone tell me why verifying the layout against the schematic is important?

It ensures the design is correct before fabrication, reducing errors.

Exactly! LVS helps ensure that the physical implementation of the circuit matches the intended functionality. It verifies that all connections and components are as they should be.

What happens if LVS violations occur?

Great question! LVS violations indicate there are mismatches, such as incorrect connections or misplaced components, which can lead to functionality issues in the final chip.

Tools Used for LVS

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's look at the tools used for LVS. Common ones include Cadence Virtuoso, Mentor Graphics Calibre, and Synopsys IC Validator. Why do you think we use automated tools for this process?

Because they can quickly and accurately check the layouts against the schematic.

That's correct! Automation speeds up the verification process and minimizes human error.

Do these tools provide reports for the errors they find?

Yes! They generate detailed reports highlighting any discrepancies, allowing designers to rectify issues efficiently.

Understanding LVS Violations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s talk about LVS violations in detail. Can anyone give me an example of what might cause an LVS violation?

If a transistor is connected incorrectly in the layout compared to the schematic?

That's a perfect example! Such errors can lead to circuit malfunction. Violations must be resolved for the chip to function correctly.

Are all LVS violations critical?

Not all violations are equally severe, but generally, any violation should be addressed to maintain integrity in the design.

The Importance of LVS in the Design Process

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, let’s summarize the importance of LVS. Why is it crucial in the overall design process?

Because it validates the layout, helping us find mistakes before the chip is fabricated.

Exactly! It serves as a safeguard against potentially costly errors in manufacturing. Would anyone like to add anything?

It's also a step that can save time in the long run by preventing issues later.

Absolutely! A thorough LVS process pays off by ensuring design correctness and efficiency in the VLSI design workflow.

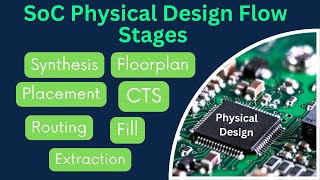

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

LVS checks for discrepancies between a circuit's physical layout and the logical schematic design. It is crucial for identifying potential errors in component placement or connectivity, which can lead to functional issues in the final product.

Detailed

Detailed Summary

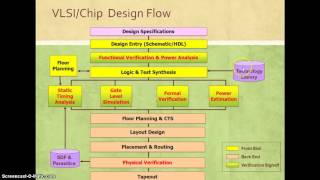

Layout Versus Schematic (LVS) is a vital verification process in physical design verification of VLSI circuits, ensuring that the physical layout matches the logical schematic. This process checks the connectivity of components in the layout against the schematic netlist. When discrepancies arise, such as incorrect connections or the wrong transistor being placed, LVS violations are flagged. The tools used for LVS include industry standards like Cadence Virtuoso, Mentor Graphics Calibre, and Synopsys IC Validator, which automatically compare the layout to the schematic, generating reports of any found discrepancies. This step is pivotal in identifying errors that could compromise the chip's functionality and helps in mitigating risks during manufacturing.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of LVS

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Layout Versus Schematic (LVS) is a verification step that ensures that the physical layout of the circuit matches the intended logical schematic. LVS checks for discrepancies between the layout and the netlist, ensuring that the connectivity of components in the layout is consistent with the schematic design.

Detailed Explanation

LVS is a crucial process in VLSI design that verifies if the actual physical design of the chip matches the original schematic diagram that designers intended. It compares the layout (where components are placed physically) with the schematic (which shows how components are connected logically). If everything matches, the design is on the right path; if there are discrepancies, these need to be fixed to avoid functional errors in the chip.

Examples & Analogies

Think of LVS like checking a building blueprint against the completed construction. If the blueprint shows a window in a specific location, but the actual building doesn’t have that window, it’s a mismatch. Just like this construction check ensures the building is as planned, LVS checks ensure that the chip is built according to its specifications.

LVS Violations

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

LVS violations occur if there are mismatches between the layout and the schematic. This can happen if, for example, the wrong transistor is placed or connected in the layout, leading to functional errors in the circuit.

Detailed Explanation

LVS violations point out specific errors in the layout compared to the schematic. For instance, if a designer intended to place a particular transistor in one position, but mistakenly placed it in a different location or connected it improperly, this would trigger an LVS violation. Such violations can result in the circuit not working as desired, which is why it is essential to identify and rectify these mismatches before moving forward in the design process.

Examples & Analogies

Consider LVS violations like having the wrong address on a letter. If you mean to send a birthday card to your friend's house but accidentally write the address of a different friend, the letter won't reach the intended person. Similarly, in LVS, if connections in the layout don't match the designated connections in the schematic, the circuit won't function correctly.

Tools for LVS

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

LVS is performed using tools like Cadence Virtuoso, Mentor Graphics Calibre, and Synopsys IC Validator that compare the layout and the schematic netlist and generate reports highlighting discrepancies.

Detailed Explanation

Several software tools automate the LVS process, making it more efficient and accurate. These tools compare the layout design against the schematic design automatically. After conducting the comparison, they generate detailed reports that highlight any discrepancies found, allowing engineers to quickly address issues. By using these specialized tools, designers can ensure high accuracy and save time in the verification process.

Examples & Analogies

Using LVS tools is akin to a quality check in a factory. Just as a quality inspector uses specific tools to check whether products are made according to the specifications, LVS tools perform checks on chip designs to ensure that they match the intended design. If the inspector finds defects, they generate a report that lists the problems; similarly, LVS tools report the mismatches they find.

Key Concepts

-

LVS Importance: Ensures circuit layout and schematic match to prevent functional errors.

-

LVS Tools: Automated software that conducts LVS checks and generates reports.

-

LVS Violations: Errors identified when layout does not conform to schematic design, impacting circuitry.

Examples & Applications

Example of an LVS violation: A layout shows a NAND gate connected improperly to a flip-flop, leading to incorrect functionality.

Example of a successful LVS process: After running LVS, a report confirms that all connections in the layout correctly match the schematic netlist, indicating readiness for fabrication.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Check your layout, give it a try, LVS will ensure no errors fly by.

Stories

Imagine a circuit where transistors are like puzzle pieces; LVS ensures every piece fits perfectly on the board.

Memory Tools

Remember LVS: Lay (for Layout), Verify (for Verification), Schematic (stay connected).

Acronyms

LVS = Layout Validation System; a system to validate layouts.

Flash Cards

Glossary

- Layout Versus Schematic (LVS)

A verification process that compares a circuit's physical layout with its logical schematic to ensure correctness.

- LVS Violations

Discrepancies found between the layout and schematic that can lead to circuitry errors.

- Netlist

A list specifying the components in a circuit along with the connections between them.

- Tools for LVS

Software applications like Cadence Virtuoso, Mentor Graphics Calibre, and Synopsys IC Validator used to automate the LVS process.

Reference links

Supplementary resources to enhance your learning experience.