Scaling Trends in FinFET Technology

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to FinFET Technology

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we’re discussing FinFET technology and how it allows us to continue following Moore’s Law. Can anyone tell me why FinFETs are important in semiconductor technology?

They help to reduce power consumption while maintaining high performance, right?

Exactly! FinFETs improve control over short-channel effects which is vital as we shrink transistor sizes. Now, what are the different technology nodes where FinFETs have been adopted?

22nm, 14nm, 10nm, and even down to 5nm.

Correct! Each of those nodes represents significant advancements. The usage started with Intel and GlobalFoundries at 22nm and reached peak performance at 3nm. Great job!

Key Scaling Goals in FinFET Technology

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s discuss the key scaling goals for FinFETs. Can anyone list a few?

Smaller fin pitch and shorter gate lengths?

Exactly! Smaller fin pitch helps pack more fins in a limited area, which is crucial. Why do you think shorter gate lengths are important?

Shorter gate lengths reduce the time it takes for a signal to travel, improving speed.

Absolutely right! Also, lowering the supply voltage is critical for reducing power consumption and heat generation. Remember the acronym SGLD: Small fin pitch, Gate length reduction, Lower VDD, Better gate control, for these goals.

Challenges in FinFET Scaling

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

We have discussed the scaling goals. Now, let’s look at some challenges FinFETs face. What do you think some of these limitations are?

Maybe the complexity and cost of the manufacturing process?

Very good! The complexity of the 3D fabrication increases costs. What else?

Variability and mismatch in performance due to tiny changes in the dimensions.

Exactly! Variability is critical as it impacts yield. Another point is the electrostatic limits that hinder performance at smaller scales. This is a common weakness for many technologies.

Future Trends Beyond FinFET

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

What might come after FinFETs? We must think ahead to sustain performance improvements.

Could it be technologies like GAAFETs or nanosheet FETs?

Yes! GAAFETs provide better gate control. It's crucial to consider how emerging technologies can overcome the limitations we discussed earlier.

What’s the significance of these new technologies?

They promise to maintain the pace of scaling, enabling even smaller transistors while improving performance and energy efficiency.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

FinFET technology has facilitated the advancement of semiconductor performance, particularly in nodes below 22nm. This section outlines the milestones of FinFET adoption across various technology nodes and identifies the key scaling goals, which include reducing fin pitch and gate lengths, lowering voltage for power efficiency, and improving gate control.

Detailed

Scaling Trends in FinFET Technology

FinFET technology is a critical enabler for keeping pace with Moore’s Law in semiconductor miniaturization. As of the section reviewed, FinFETs have been successfully utilized in several technology nodes:

- 22nm: First mass production of FinFETs by companies like Intel and GlobalFoundries.

- 14nm/16nm: Marked the mainstream adoption phase across companies such as Intel, TSMC, and Samsung.

- 10nm/7nm: This period is noted for high-volume production, continuing to set benchmarks in the industry.

- 5nm/3nm: Recognized as the peak performance phase for FinFET devices.

Key scaling goals within this technology include:

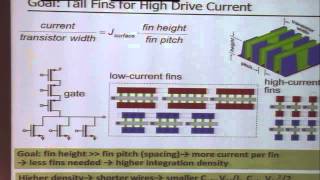

- Smaller Fin Pitch: This refers to reducing the distance between fins, allowing for more fins within the same area.

- Shorter Gate Lengths (Lg): Aim to decrease gate lengths to enhance electronic performance.

- Lower VDD: A focus on reducing the supply voltage to minimize power consumption.

- Better Gate Control: Utilizing multi-gate structures to improve performance and reduce leakage.

- Higher Drive Current: Achieved by increasing fin height, which improves overall device efficiency.

Despite these advancements, it is important to acknowledge that FinFETs are pushing towards their scaling limits, and challenges remain as we look beyond FinFET technology.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Adoption Across Technology Nodes

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

FinFETs have been widely adopted in advanced nodes:

Technology Foundry Examples FinFET Adoption

Node

22nm Intel, GlobalFoundries First mass FinFET usage

14nm/16nm Intel, TSMC, Samsung Mainstream adoption

10nm / 7nm TSMC, Samsung, Intel High-volume production

5nm / 3nm TSMC, Samsung Peak FinFET performance

Detailed Explanation

FinFET technology has been progressively adopted in various node sizes. Starting from 22nm, major companies like Intel and GlobalFoundries began using FinFETs in mass production. As technology advanced, by the 14nm and 16nm nodes, companies such as Intel, TSMC, and Samsung adopted it as standard practice, signifying mainstream acceptance. As the technology matured, nodes reached 10nm and 7nm where high-volume production was achieved. Finally, at 5nm and 3nm, FinFETs peaked in performance, representing the forefront of current semiconductor technology.

Examples & Analogies

Think of FinFET adoption like the evolution of smart phones. Initially, older models (22nm) laid the groundwork for cutting-edge features (14nm and 16nm), leading to commonly used smartphones (10nm and 7nm) that have significantly enhanced capabilities and performance by the time we reach the modern devices (5nm and 3nm). Just as smartphones have transformed with advanced technology, so too have FinFETs evolved in the semiconductor industry.

Key Scaling Goals

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Key Scaling Goals:

● Smaller Fin Pitch (distance between fins)

● Shorter Gate Lengths (Lg)

● Lower VDD for power reduction

● Better gate control using multi-gate structures

● Higher drive current with taller fins

Detailed Explanation

The scaling of FinFET technology targets several key goals to enhance performance. Smaller fin pitch means reducing the distance between the individual fins, allowing for more fins in a given area which improves performance. Shorter gate lengths (Lg) lead to faster switching speeds. Lower VDD (voltage supply) is aimed at reducing power consumption. Better gate control through multi-gate structures helps to control the channel more effectively, mitigating leakage current and improving efficiency. Finally, taller fins enable higher drive currents, boosting processing power without sacrificing energy efficiency.

Examples & Analogies

Imagine trying to fit more cars on a road. Making the distance between lanes smaller (smaller fin pitch) allows you to add more lanes without increasing the overall road width, enabling more cars (fins) to operate efficiently. Shorter cars (shorter gate lengths) can also move faster through these lanes. Reducing the speed limit (lower VDD) cuts down on fuel consumption, while better traffic control measures (better gate control) ensure that all cars can flow smoothly. Taller vehicles (higher drive current) can carry more loads, thereby increasing highway productivity without needing to expand the roads.

Key Concepts

-

FinFET Adoption: Key milestones in FinFET technology from 22nm to 5nm technology nodes highlight the evolving landscape of semiconductor manufacturing.

-

Key Scaling Goals: Smaller fin pitches, shorter gate lengths, lower supply voltage (VDD), enhanced gate control, and increased drive current are essential targets for FinFET scaling.

-

Challenges: Factors like quantized channel width, process complexity, variability, electrostatic limits, and parasitic capacitance pose significant hurdles in further scaling of FinFET technology.

Examples & Applications

Example of FinFET Adoption: Intel's transition from 22nm to 14nm processes utilizing FinFETs to enhance performance and reduce power consumption in CPUs.

Example of Scaling Goals: The need to achieve a lesser than 10nm gate length in FinFETs to keep pace with increasingly demanding performance requirements from modern applications.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

FinFETs are neat, make devices fleet, smaller and smarter, innovation they greet.

Stories

Once upon a time in the world of semiconductors, FinFETs emerged to solve the mysteries of shrinking sizes, holding hands with innovation while overcoming obstacles like complex processes and cost.

Memory Tools

Use SGLD (Small fin pitch, Gate length, Lower VDD) to remember FinFET’s scaling goals!

Acronyms

Use 'SGLD' as an acronym to recall the scaling goals in FinFET technology.

Flash Cards

Glossary

- FinFET

A type of multi-gate MOSFET that has improved control over the channel, allowing for lower power consumption and diminished short-channel effects.

- Fin Pitch

The distance between adjacent fins in a FinFET device; smaller pitch allows for higher integration density.

- Gate Length (Lg)

The length of the gate electrode in a transistor; shorter gate lengths improve device speed.

- VDD

The supply voltage for digital circuits, where lower values help to reduce power consumption.

- Electrostatic Limits

The limitations related to electrostatic control of carriers within transistors as the devices scale down.

- Shortchannel Effects

Phenomena that occur in MOSFETs when the channel length is reduced to the point where the control of the gate over the channel becomes reduced, affecting performance.

- Yield

The percentage of functional chips obtained from a wafer in semiconductor fabrication.

Reference links

Supplementary resources to enhance your learning experience.