Case Studies in VHDL/Verilog Design

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Overview of Case Studies

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we’re examining two important case studies in VHDL and Verilog design. What do you think the purpose of these case studies is, Student_1?

I think they help us understand how the languages are applied in real projects.

Exactly! They reveal the practical challenges and solutions in designing complex systems. Student_2, why might design challenges arise?

Challenges like timing closure and resource management can affect how the system functions.

Great point! Remember, we can think of timing closure as ensuring all signals reach their destination on time, which is critical in FPGA designs!

So design solutions would be how we overcome these obstacles?

Absolutely! Each case study will reveal specific solutions for those challenges.

FPGA-Based Digital System Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive into the first case study: an FPGA-based digital system design. What was the main goal of this project, Student_4?

It was to create a custom communication protocol for a wireless sensor network.

Correct! Now let's discuss challenges. Student_1, what challenges did they encounter?

They faced timing closure and needed to implement error detection.

Exactly. Imagine timing closure like a race where the signals must not fall behind. Student_3, what might be a design solution for error detection?

They could add checksums or parity bits to the protocol.

Spot on! Integration of error correction strategies enhances reliability in communication systems.

ASIC Design for Mobile Devices

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Moving on to the second case study, we will look at ASIC design for mobile devices. What were the key considerations in designing the power management system, Student_2?

They had to optimize for power efficiency and minimize chip area.

Right! Let’s think about power efficiency as keeping the device cool while it performs its tasks. Student_4, what is a potential issue with shrinking chip size?

It might lead to higher thermal output and affect performance!

Exactly! They must balance efficiency with performance to avoid overheating. Summarizing this, proper design can lead to more compact and efficient devices.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore two case studies on the design of an FPGA-based digital system and an ASIC for mobile devices, highlighting the design challenges encountered, such as timing closure and power efficiency, along with the corresponding solutions utilizing VHDL and Verilog.

Detailed

Case Studies in VHDL/Verilog Design

This section dives into real-world case studies that showcase the practical application of VHDL and Verilog in digital system design, providing students with insights into design challenges and the solutions employed.

Case Study 1: FPGA-Based Digital System Design

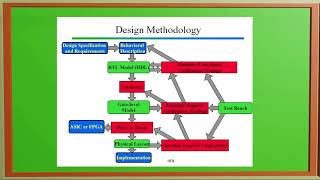

Here we examine a project focused on designing an FPGA-based system with a custom communication protocol for a wireless sensor network. Key design challenges include:

- Timing Closure: Ensuring that the design meets the required timing specifications.

- Efficient FPGA Resource Use: Implementing the design to optimize FPGA resource allocation.

- Error Detection and Correction: Adding mechanisms to enhance communication reliability.

Design Solution: The project demonstrates the implementation of a robust communication system using VHDL or Verilog to satisfy specifications and perform efficiently on an FPGA.

Case Study 2: ASIC Design for Mobile Devices

In this case study, VHDL or Verilog is utilized for designing an ASIC focused on power management for mobile devices. Key design challenges include:

- Power Efficiency: Balancing performance while minimizing power consumption.

- Chip Area Optimization: Ensuring that the design fits within a compact form while meeting performance needs.

- Thermal Constraints: Maintaining device reliability under operational thermal conditions.

Design Solution: The use of Verilog allowed for the integration of multiple power management circuits into a small form factor while ensuring efficient operation within a mobile device.

These case studies highlight the significance of understanding design considerations in VHDL and Verilog implementations and serve as valuable references for future digital system design projects.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Case Study 1: FPGA-Based Digital System Design

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

A case study of designing an FPGA-based system using VHDL or Verilog. The project involves designing a custom communication protocol for a wireless sensor network.

● Design Challenges:

○ Timing closure and efficient use of FPGA resources.

○ Implementing error detection and correction mechanisms in the communication protocol.

● Design Solution:

Using VHDL or Verilog, implement a robust communication system that meets the required specifications and performs efficiently on an FPGA.

Detailed Explanation

This case study focuses on the development of a digital system that utilizes an FPGA, which is a type of hardware used for creating electronic circuits. In this project, the goal is to design a custom communication protocol that allows a wireless sensor network to communicate effectively.

The project faces several design challenges, including 'timing closure,' which refers to ensuring that signals arrive at the right time within the circuit to avoid errors, and efficient use of FPGA resources, which means making the best use of the limited space and components available in the FPGA. Other concerns include implementing error detection and correction mechanisms, which are strategies to identify and fix any mistakes that occur during data transmission.

To achieve these goals, the designer can use VHDL or Verilog to create a communication system that meets the specifications set for the project, ensuring that it works correctly and efficiently on the FPGA.

Examples & Analogies

Imagine you are setting up a wireless network for a new smart home. To ensure that everything communicates properly—a thermostat signals to a heater, a smoke detector alerts the system—you need to establish a clear, reliable communication protocol. You might need to troubleshoot when devices miss messages or respond at the wrong times, similar to how timing issues must be resolved in FPGA designs.

Case Study 2: ASIC Design for Mobile Devices

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this case study, VHDL or Verilog is used to design an ASIC for a mobile device's power management system.

● Design Challenges:

○ Optimizing for power efficiency and minimal chip area.

○ Ensuring high-speed performance while meeting thermal constraints.

● Design Solution:

Using Verilog, design an ASIC that integrates multiple power management circuits into a small form factor, ensuring efficient operation in a mobile device.

Detailed Explanation

This case study involves designing an ASIC (Application-Specific Integrated Circuit) specifically for managing power in mobile devices, which is crucial for enhancing battery life and performance. The designer must consider several important challenges:

- Power Efficiency: The ASIC should consume as little power as possible to prolong battery life, which is particularly vital for mobile devices that rely on their rechargeable batteries.

- Chip Area: The design must fit into a small space while integrating multiple power management circuits, which means careful planning of the layout and design.

- High-Speed Performance: The circuitry must operate quickly to meet the performance needs of mobile applications without generating too much heat, which can impair device efficiency and longevity.

To meet these challenges, Verilog can be used to design the ASIC, ensuring that it is compact and efficiently manages power while maintaining high performance.

Examples & Analogies

Think of an ASIC design like creating a highly efficient engine for a compact car. You want the engine to deliver high performance (speed) while using as little fuel (power) as possible and fitting into a small engine compartment (minimal chip area). You must balance all these factors to ensure the car runs smoothly without overheating and while making the best use of the available space.

Key Concepts

-

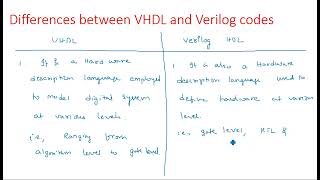

VHDL and Verilog are used for designing both FPGA and ASIC systems.

-

Design challenges can include timing closure, resource optimization, and power efficiency.

-

Practical case studies illustrate how theoretical concepts are applied in real-world situations.

Examples & Applications

In the FPGA-based design, the implementation of a communication protocol addressed specific timing and resource challenges.

The ASIC design for mobile devices integrated multiple power management circuits within a compact framework to address power efficiency.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When designing chips that do the heavy lift, remember timing and power must be your gift.

Stories

Imagine a racing car where every part must work precisely together; that's how we ensure timing closure in designs to avoid chaos on the track.

Memory Tools

To remember key ASIC design factors: PCT - Power efficiency, Chip area, Thermal management.

Acronyms

Use **ERC** for Easy Recall

Error checking

Resource use

Communication protocols.

Flash Cards

Glossary

- FPGA

Field-Programmable Gate Array; an integrated circuit that can be programmed for a specific application.

- ASIC

Application-Specific Integrated Circuit; a chip designed for a specific application, optimizing for performance and efficiency.

- Timing Closure

The process of ensuring that all signals in a circuit meet their timing requirements.

- Error Detection

Techniques used to identify errors in data transmission or processing.

- Power Management

Strategies and circuits designed to optimize a device’s power consumption.

Reference links

Supplementary resources to enhance your learning experience.