VHDL in FPGA and ASIC Design

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to VHDL in FPGA and ASIC Design

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we'll explore how VHDL is used in FPGA and ASIC design. Can anyone tell me what FPGA stands for?

Doesn't it stand for Field-Programmable Gate Array?

Exactly, Student_1! FPGAs are reprogrammable silicon chips, which means we can use VHDL to customize their functionality. Let's discuss the key design considerations we must keep in mind.

What kind of considerations are we talking about?

Great question! Two essential considerations are resource utilization and timing analysis. Resource utilization focuses on efficiently using logic blocks and I/O pins. Timing analysis ensures that our circuit meets speed and performance criteria. Remember the acronym 'R.U.' for 'Resource Utilization'!

How do you optimize resource usage in VHDL?

We'll get to that soon, but typically, simplifying designs while keeping performance in mind is key. Let's look at a practical project using VHDL.

What's the project about?

We will implement a simple shift register and test its functionality on an FPGA. This will show how we can apply the concepts we learn here. Let's summarize: VHDL aids FPGA and ASIC design by ensuring we consider resource usage and timing analysis.

Taking a Deeper Look at Design Considerations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we know the basic concepts, let's take a deeper look at these design considerations. What do you think is the impact of proper timing analysis?

It probably prevents errors in the design, right?

Absolutely! If timing is not accounted for, we may face issues like race conditions or setup/hold time violations. Who can explain what a shift register is?

It's a device that shifts its bits with each clock cycle.

Correct! It’s essential when working with serial data shares. When implementing the shift register, we must ensure efficient use of FPGA resources. What resources would we be considering here?

Logic blocks and I/O pins, right?

Exactly! Let’s remember: efficient resource usage maximizes performance while keeping costs down. Now let's summarize today's discussion.

Practical Implementation Example

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

For our project, we will implement a simple shift register. Can anybody elaborate on what steps we might take to implement this in VHDL?

We would start by defining the shift register's behavior, right?

Correct! We would define how the register accepts input and shifts bits on each clock edge. What else should we consider before we start implementation?

Definitely timing analysis to ensure it works as expected!

Exactly, Student_1! Additionally, we'll have to validate our design on an FPGA after creating it. Testing on the FPGA will also confirm that we've optimized resource usage effectively. Anyone can recap the significance of VHDL in these projects?

VHDL helps us design, simulate, and optimize our circuits before physical implementation.

Right! Excellent recap! Remember the importance of VHDL in both FPGA and ASIC environments.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, the role of VHDL in FPGA and ASIC design is explored, emphasizing how VHDL is utilized for efficient resource management, timing analysis, and practical projects such as implementing a shift register on an FPGA.

Detailed

VHDL in FPGA and ASIC Design

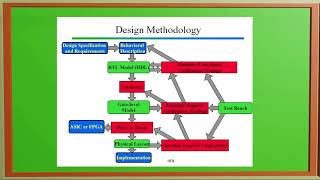

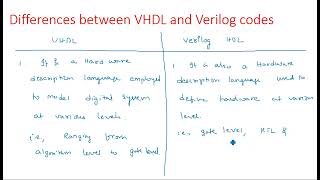

VHDL (VHSIC Hardware Description Language) plays a crucial role in the design of Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs). This section discusses essential design considerations for using VHDL in these two areas.

Design Considerations

- Resource Utilization: Efficient use of FPGA resources, such as logic blocks and Input/Output (I/O) pins, is vital. Designers must consider how to minimize resource usage while still achieving desired performance.

- Timing Analysis: Ensuring that the circuit meets required speed and performance constraints is essential. Timing analysis helps validate the design's performance before hardware implementation.

Project Work Example

One practical example provided is the implementation of a simple shift register using VHDL, followed by testing its functionality on an FPGA platform. This project requires optimizing the design for resource usage and clock speed, demonstrating how theoretical principles are applied in real-world scenarios.

Overall, understanding how VHDL operates in FPGA and ASIC design is critical for engineers and designers looking to maximize performance and resource efficiency in their projects.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to VHDL in FPGA and ASIC Design

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

VHDL is frequently used for programming FPGAs (Field-Programmable Gate Arrays) and designing ASICs (Application-Specific Integrated Circuits).

Detailed Explanation

VHDL is a hardware description language that plays a crucial role in both FPGA and ASIC design. FPGAs are reconfigurable hardware, allowing designers to program their functionality after manufacturing. In contrast, ASICs are custom chips designed for specific applications. VHDL provides a means to describe the intended behavior and structure of these hardware designs, ensuring that they meet specific requirements for performance and functionality.

Examples & Analogies

Think of VHDL as a recipe used by chefs (engineers) to create dishes (hardware designs). For an FPGA, the chef can change the dish based on the available ingredients (modifiable logic resources). For an ASIC, the chef uses a fixed set of ingredients to make a specific dish that is ordered by customers (tailored functionality).

Design Considerations in VHDL for FPGA and ASIC

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Design Considerations:

- Efficient use of FPGA resources, including logic blocks and I/O pins.

- Timing analysis to ensure that the circuit meets speed and performance constraints.

Detailed Explanation

When designing with VHDL for FPGAs and ASICs, several important considerations arise. First, using FPGA resources efficiently means making the most of the available logic blocks and input/output pins. This ensures that the design operates within the constraints of the hardware. Second, timing analysis is essential as it evaluates whether the circuit can operate at the desired speeds. If timing constraints are not met, the design may fail, so engineers must check that signals propagate through the circuit quickly enough to avoid delays.

Examples & Analogies

Imagine building a bridge (the FPGA design) that can support cars (signals) crossing without delays. You need to ensure the bridge (resources) is wide enough (efficient use) and that cars can cross it within a certain time (timing analysis). If too many cars try to cross (insufficient resources), traffic will build up, causing delays.

Project Work Example: Shift Register Implementation

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Project Work Example:

Implement a simple shift register using VHDL and test its functionality on an FPGA platform, optimizing for resource usage and clock speed.

Detailed Explanation

A project example could involve designing a shift register, which is a type of data storage element used in digital circuits. The goal would be to implement this shift register using VHDL on an FPGA. The design process would include writing the VHDL code to describe how data is input, stored, and shifted through the register. Additionally, the designer would test the functionality to ensure that data shifts correctly and optimize the design for efficient use of FPGA resources and maximizing clock speed, which directly impacts performance.

Examples & Analogies

Think of a shift register like a line of people passing a message down the line. Each person (flip-flop) holds the message for a moment and then passes it to the next. The goal is to ensure everyone passes the message quickly and efficiently without dropping it. Testing the design ensures that every person can hear and pass the message properly, similar to how we ensure that the shift register functions correctly with data.

Key Concepts

-

Resource Utilization: Efficient use of FPGA resources is crucial for design effectiveness.

-

Timing Analysis: Necessary for ensuring that the circuit meets speed and performance constraints.

-

Shift Register: A digital memory circuit that is important for data manipulation.

-

VHDL: A fundamental language employed in the design and simulation of digital circuits.

Examples & Applications

Designing a simple shift register using VHDL and simulating its function on an FPGA.

Conducting timing analysis to ensure circuit performance meets specifications.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

FPGA, play it your way—Program it right, every day!

Stories

Imagine a factory where machines (FPGA) can be reprogrammed to produce various products, adapting its function on the fly, just like we adapt VHDL in design.

Memory Tools

R.U.T: Remember Utilization and Timing for FPGA designs!

Acronyms

VHDL

Versatile Hardware Design Language.

Flash Cards

Glossary

- VHDL

A VHSIC Hardware Description Language used for modeling digital systems.

- FPGA

Field-Programmable Gate Array; a reprogrammable silicon device used in hardware design.

- ASIC

Application-Specific Integrated Circuit; a custom-designed chip for a specific application.

- Timing Analysis

The process of verifying a design's timing constraints to ensure correct operation.

- Resource Utilization

Efficient use of hardware resources such as logic blocks and I/O pins in design.

- Shift Register

A type of digital memory circuit that shifts its data with each clock cycle.

Reference links

Supplementary resources to enhance your learning experience.